# SINGLE-CHIP SET-TOP BOX DECODER WITH MP3 AND HARD DISK DRIVE SUPPORT

### DATA SHEET

### Integrated 32-bit host CPU up to 81 MHz

• 2 Kbytes of Icache, 2 Kbytes of Dcache, and 4 Kbytes of SRAM configurable as Dcache.

### Audio decoder

- 5.1 channel Dolby Digital® /MPEG-2 multi-channel decoding, 3 X 2-channel PCM outputs

- IEC60958 -IEC61937 digital output

- SRS®/TruSurround®

- DTS® digital out and MP3 decoding

- Alignment beep for satellite dishes.

- Video decoder

- Supports MPEG-2 MP@ML

- Fully programmable zoom-in and zoom-out

- NTSC to PAL conversion.

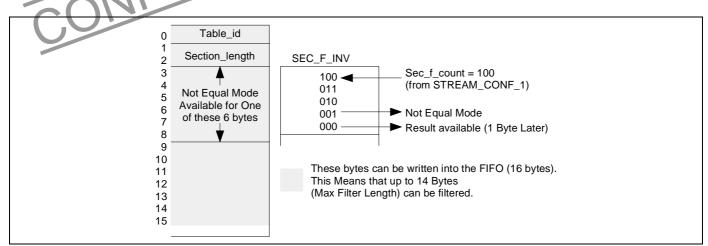

- DVD and SVCD subpicture decoder

- High performance on-screen display

- 2 to 8 bits per pixel OSD options

- Anti-flicker, anti-flutter and anti-aliasing filters.

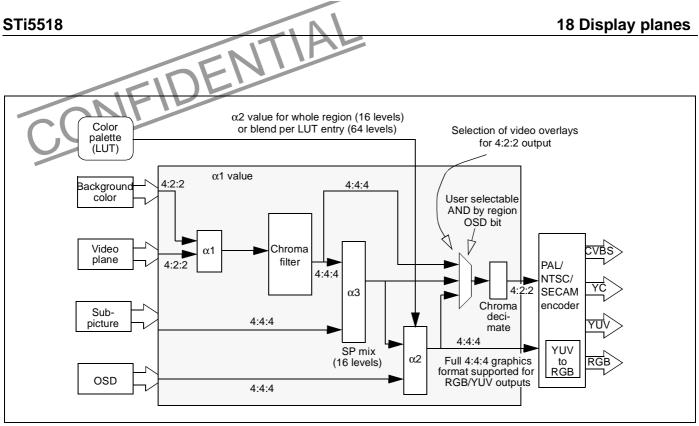

- PAL/NTSC/SECAM encoder

- RGB, CVBS, Y/C and YUV outputs with 10-bit DACs

- Macrovision® 7.01/6.1 compatible (optional).

- Shared SDRAM memory interface

- 1 or 2x16-Mbit, or 1x64-Mbit 125 MHz SDRAM.

- Programmable CPU memory interface for SDRAM, ROM, peripherals...

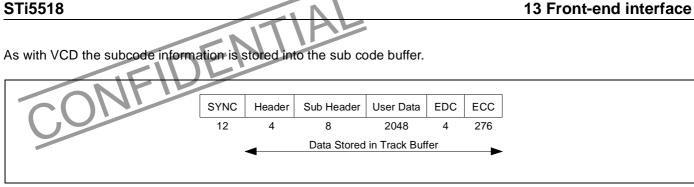

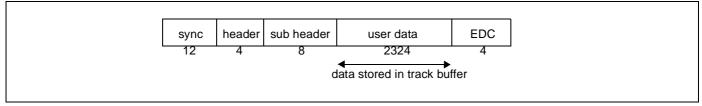

- Front-end interface

- DVD, VCD, SVCD and CD-DA compatible

- Serial, parallel and ATAPI interfaces

- Hardware sector filtering

- Integrated CSS decryption and track buffer.

- Hardware transport-stream demultiplexor

- Parallel/serial input

- DES and DVB descramblers

- 32 PID support.

- Integrated peripherals

- 2 UARTs, 2 SmartCards, I<sup>2</sup>C controller, 3 PWM outputs, 3 capture timers

- Modem support

- 44 bits of programmable I/O

- IR transmitter/receiver.

- Professional toolset support

- ANSI C compiler and libraries.

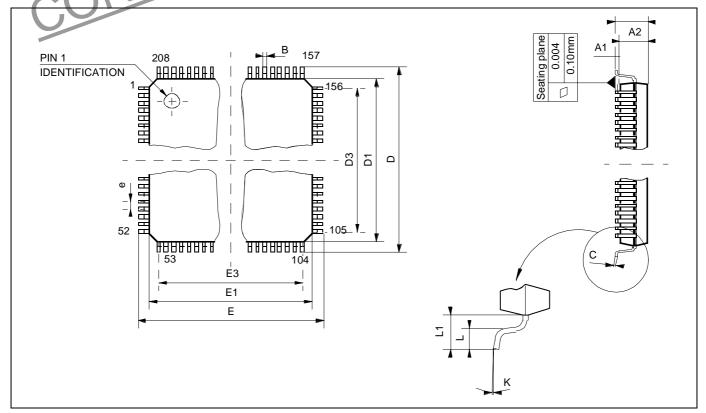

- 208 pin PQFP package.

The STi5518 is a highly integrated single-chip decoder, designed for use in feature-rich mass-market set-top boxes. It integrates a high-performance 32-bit CPU, a dedicated block for DVB/DirecTV transport demultiplexing and descrambling, modules for MPEG-2 video and audio decoding with 3D-surround and MP3 support, advanced display and graphics features, a digital video encoder and all of the system peripherals required in a typical low-cost interactive receiver.

To cover the needs of DVD-capable set-top boxes, STi5518 integration options include a CSS decryption block, a Dolby Digital audio decoder and Macrovision copy protection.

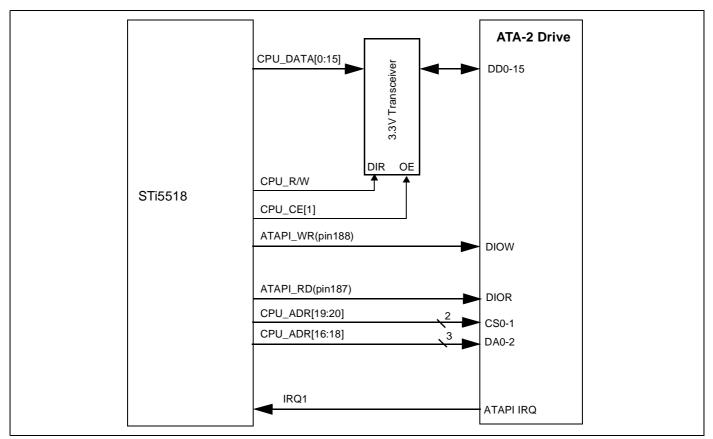

An ATAPI interface is built-in, supporting the glueless connection of standard Hard Disk Drives. In this way, the STi5518 is ideal for set-top boxes featuring trick modes such as live TV recording, pausing and time-shifting.

The STi5518 is backward compatible with the popular STi5500 set-top box decoder, allowing easy migration from the previous generation.

The high level of integration in a single PQFP-208 package makes the STi5518 ideally suited for low-cost, high-volume set-top box applications.

### 7170179 D

The information in this data sheet is subject to change without notice.

|                |                                  | STi5518 |

|----------------|----------------------------------|---------|

| Tabl           | le of contents                   |         |

| 1              | Architecture overview            |         |

| 1.1            | Introduction                     |         |

| 1.2            | Central processor                |         |

| 1.3            | MPEG video decoder               | 10      |

| 1.4            | Audio decoder                    | 11      |

| 1.5            | IR transmitter/receiver          | 11      |

| 1.6            | Modem analog front-end interface | 11      |

| 1.7            | Memory subsystem                 |         |

| 1.8            | Serial communication             |         |

| 1.9            | Front-end interface              | 13      |

| 1.10           | On-chip PLL                      | 13      |

| 1.11           | Diagnostic controller (DCU)      | 13      |

| 1.12           | Interrupt subsystem              |         |

| 1.13           | PAL/NTSC/SECAM encoder           |         |

| 1.14           | SmartCard interfaces             | 13      |

| 1.15           | PWM and counter module           | 14      |

| 1.16           | Parallel I/O module              | 14      |

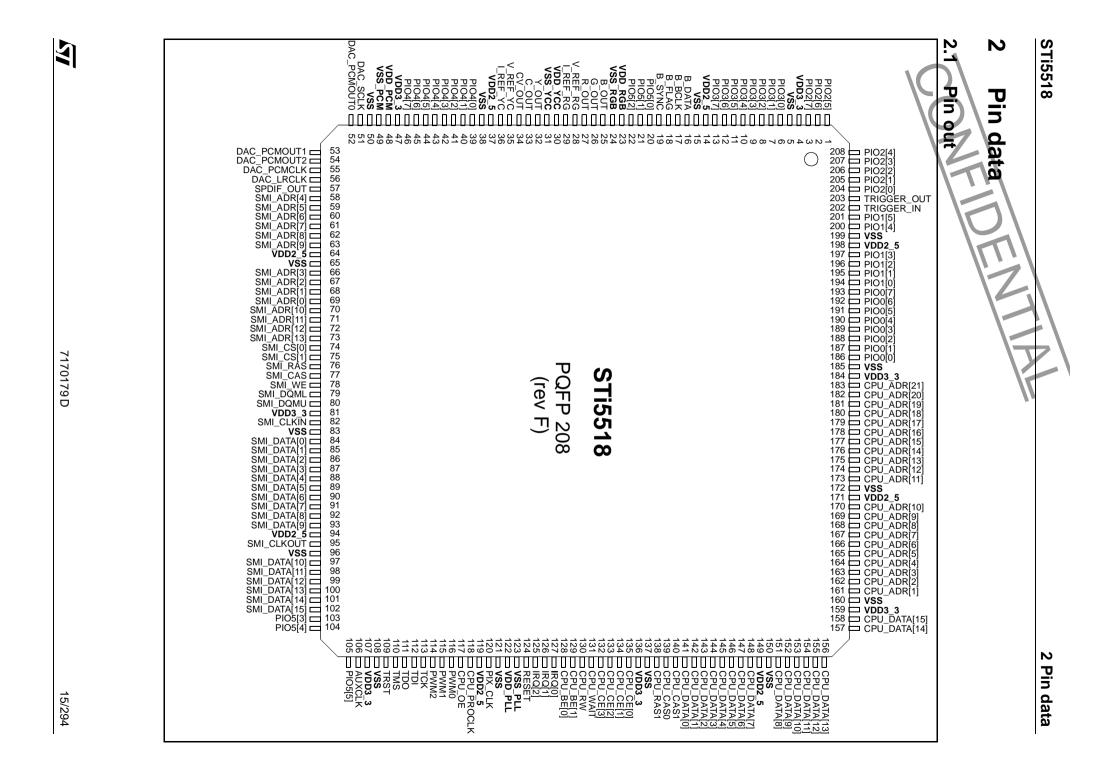

| •              | Pin data                         | 45      |

| 2              | Pin data                         |         |

| 2.1            | Pin out                          |         |

| 2.2            | •                                |         |

| 2.3            | Pins sorted by pin number        |         |

| 3              | Central processing unit          |         |

| 3.1            | Registers                        |         |

| 3.2            | Processes and concurrency        |         |

| 3.3            | Priority                         |         |

| 3.4            | Process communications           |         |

| 3.5            | Timers                           |         |

| 3.6            | Traps and exceptions             |         |

| 3.6.1          | Trap groups                      |         |

| 3.6.2<br>3.6.3 | Events that can cause traps      |         |

| 3.6.4          | Restrictions on trap handlers    | 35      |

| 4              | Instruction set                  |         |

| 4.1            |                                  |         |

| 4.2            | Instruction characteristics      |         |

| 4.3            | Instruction-set tables           |         |

|                |                                  |         |

| 5              | Interrupt system                 |         |

| 5.1            | Introduction                     |         |

| 5.2            | Interrupt controller             |         |

| 5.3            | Interrupt vector table           |         |

| 5.4            | Interrupt handlers               | 47      |

| CT:EE4         |                                              |    |

|----------------|----------------------------------------------|----|

| STi551         | <u>o</u>                                     |    |

|                |                                              |    |

| 5.5            | Interrupt latency                            | 48 |

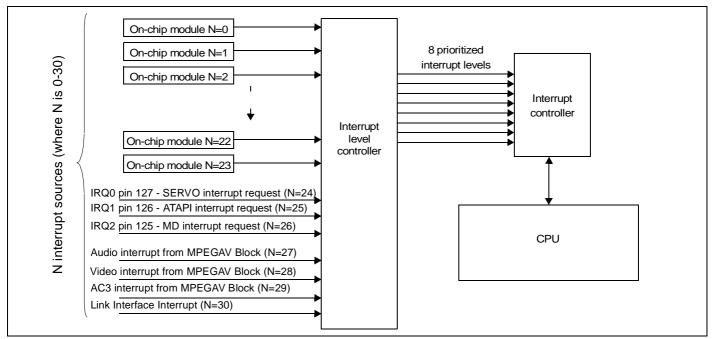

| 5.6            | Pre-emption and interrupt priority           | 48 |

| 5.7            | Restrictions on interrupt handlers           | 48 |

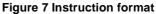

| 5.8            | Interrupt level controller                   | 49 |

| 5.9            | Interrupt assignments                        | 50 |

|                |                                              |    |

| 6              |                                              | 51 |

| 6.1            | Overview                                     | 51 |

| 6.2            |                                              | 52 |

| 6.3            | System memory use                            | 55 |

| _              |                                              |    |

| 7              |                                              | 56 |

| 7.1            |                                              | 56 |

| 7.2            | On-chip SRAM memory                          | 56 |

| 7.3            | Caching                                      | 56 |

| 7.3.1          | Outline of operation                         | 57 |

| 7.3.2<br>7.3.3 | Cache initialization                         |    |

| 7.3.3          | Data cache                                   |    |

| 7.3.5          | Instruction cache                            | 59 |

| 7.3.6          | Cacheable and non-cacheable memory locations | 60 |

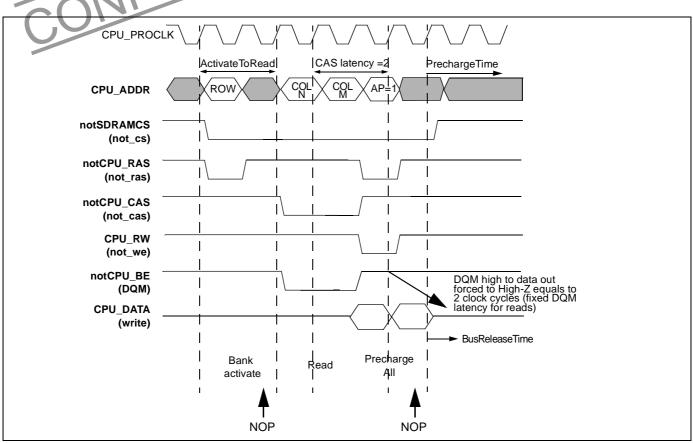

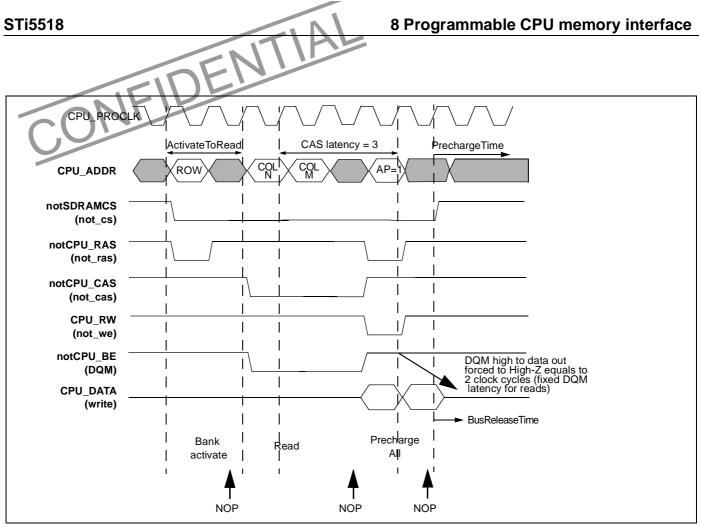

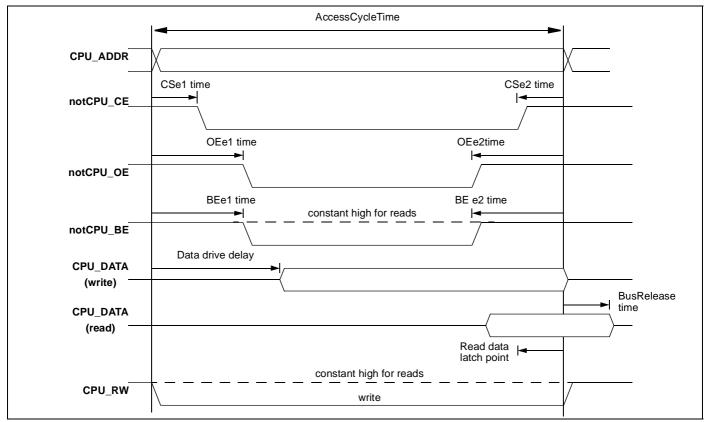

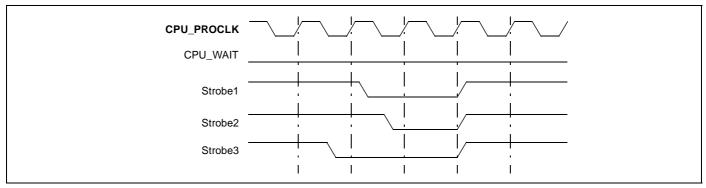

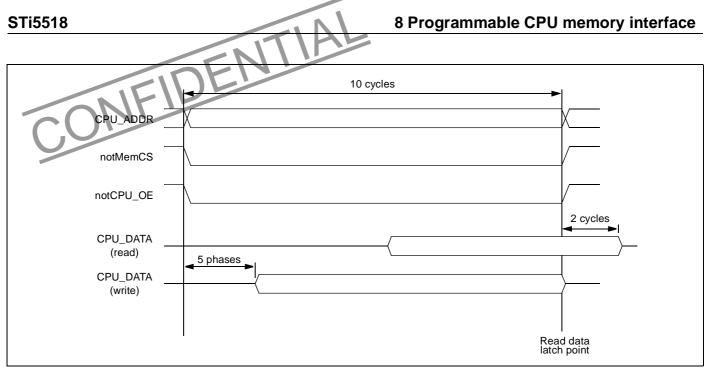

| 8              | Programmable CPU memory interface            | 63 |

| 8.1            |                                              |    |

| 8.2            | Configuration list                           | 68 |

| 8.3            |                                              | 70 |

|                |                                              |    |

| 8.3.1<br>8.3.2 | SDRAM                                        |    |

| 8.3.3          | SRAM or peripheral access cycles             | 78 |

| 8.3.4          | Wait                                         |    |

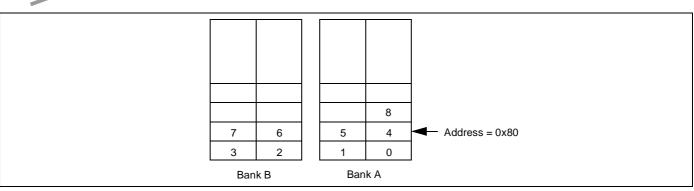

| 8.3.5          | Bank-width based address shifting            |    |

| 8.4            | EMI configuration                            |    |

| 8.5            | Default configuration                        | 80 |

| 9              | System services                              | 82 |

| <b>9</b> .1    | Power-on hard reset                          |    |

| 9.2            | Bootstrap                                    |    |

| 9.2            | Boolstrap                                    | 02 |

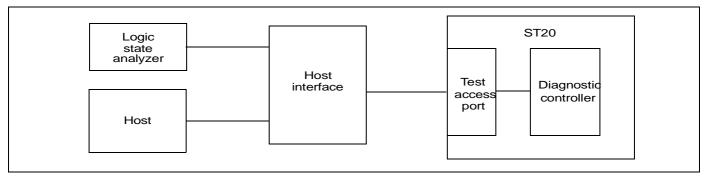

| 10             | Diagnostic controller                        | 83 |

| 10.1           | Diagnostic hardware                          | 83 |

| 10.2           | Access features                              | 84 |

| 10.3           | Software debugging features                  | 84 |

| 10.4           | Controlling the diagnostic controller        |    |

| 10.5           | Peeking and poking the host from the target  |    |

| 10.0           |                                              |    |

| 11             | Test access port                             | 88 |

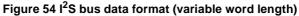

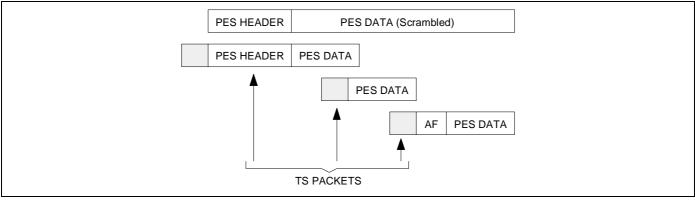

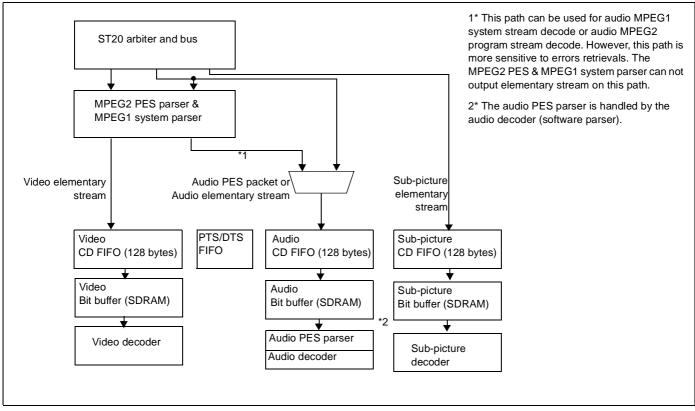

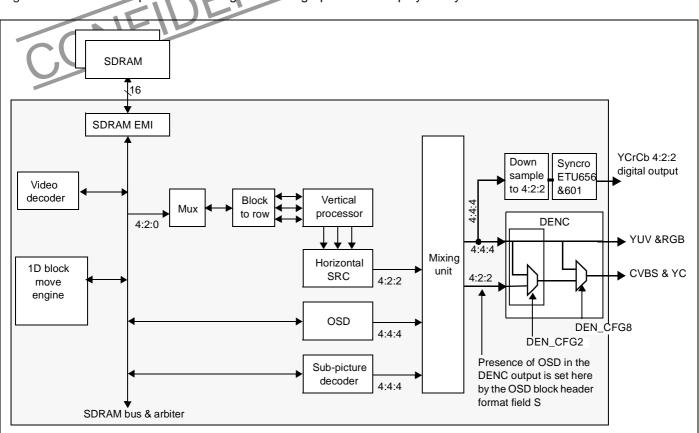

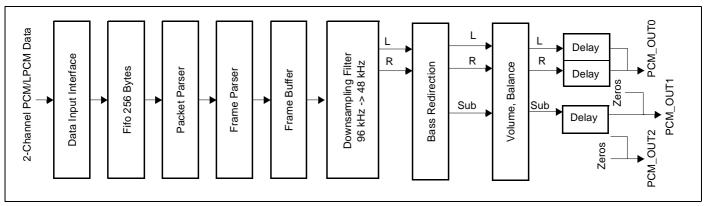

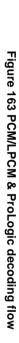

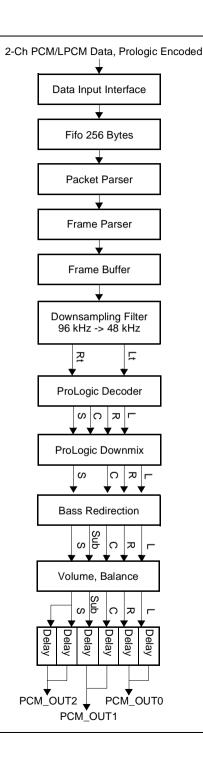

| 12             | Data flow                                    | 89 |

| 12.1           | On-chip modules                              |    |

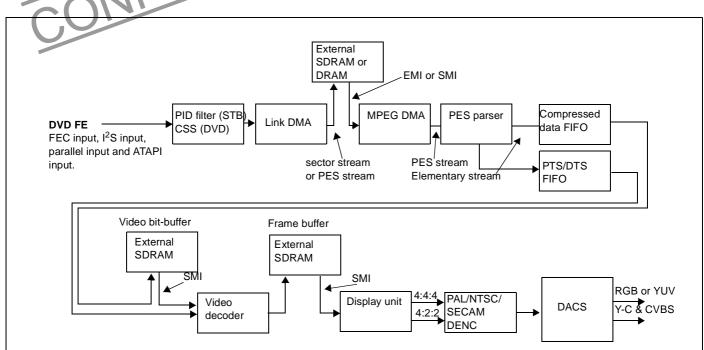

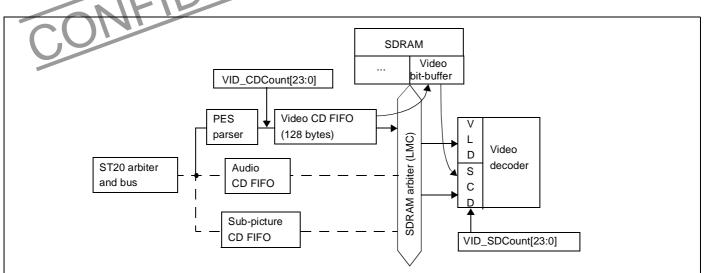

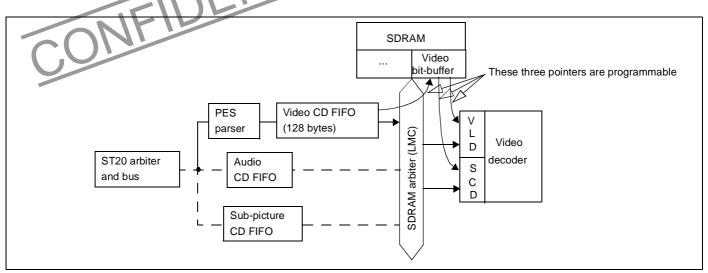

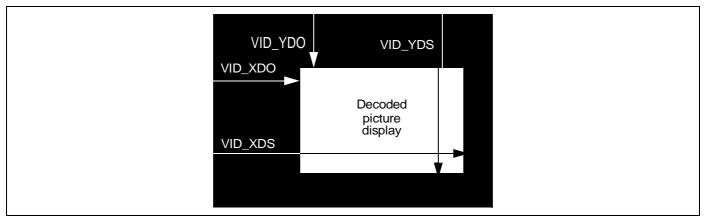

| 12.2           | Video data flow                              |    |

|                |                                              | 50 |

57

|                  |                                                      | OT'EE44    |

|------------------|------------------------------------------------------|------------|

|                  |                                                      | STi5518    |

|                  |                                                      |            |

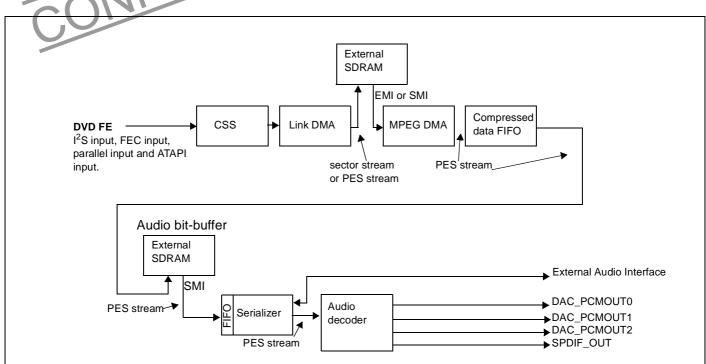

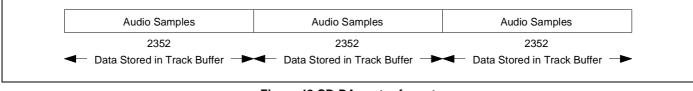

| 12.3             | Audio data flow                                      | 91         |

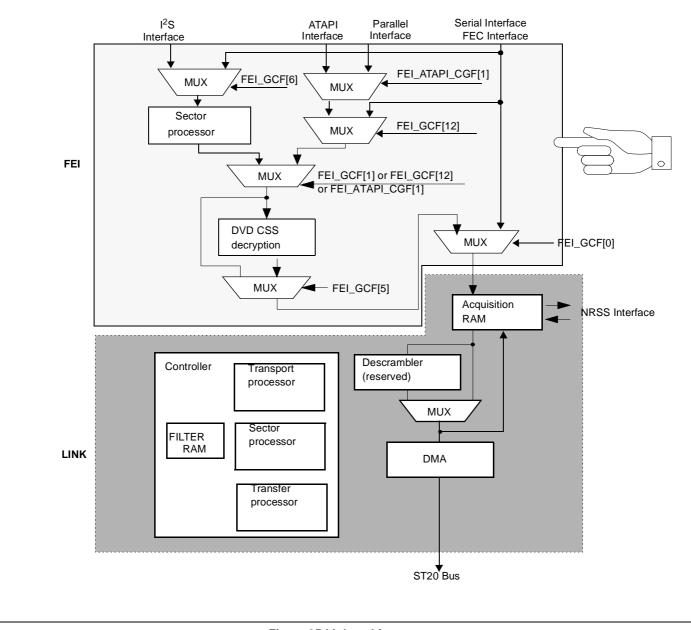

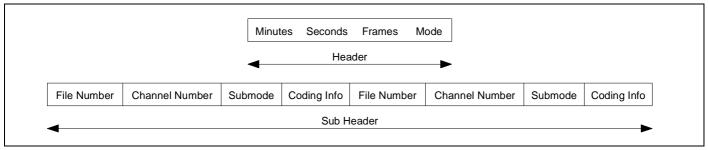

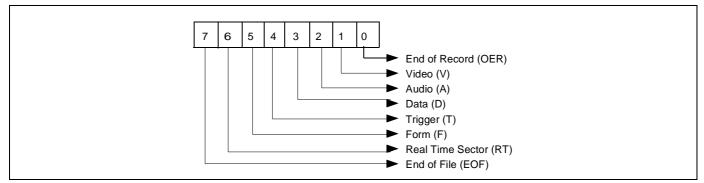

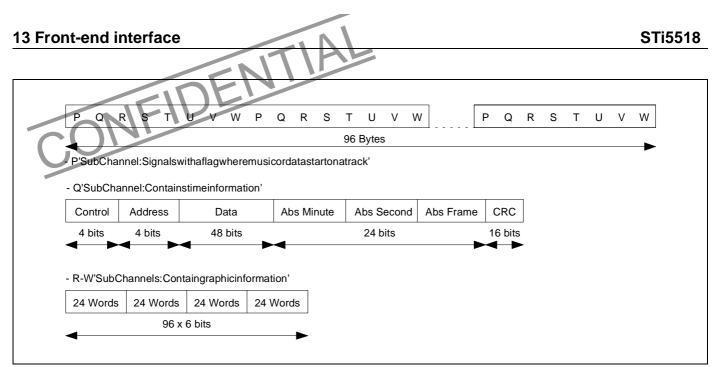

| 13               | Front-end interface                                  |            |

| 13.1             | Introduction                                         |            |

| 13.2             | Serial interface                                     |            |

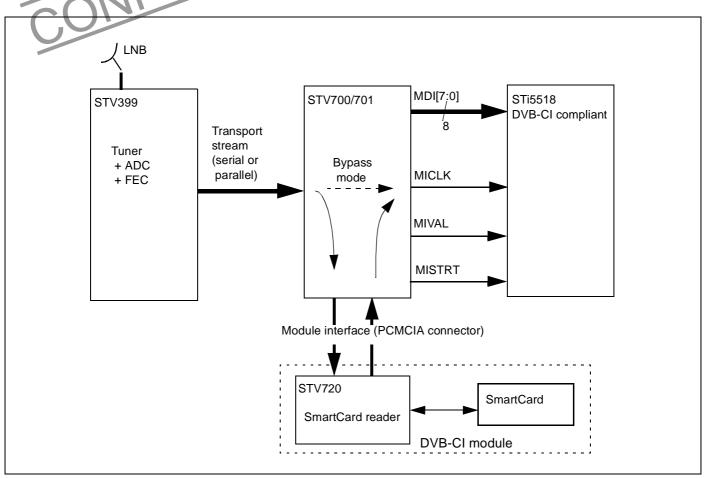

| 13.3             | DVB-CI mode (optional)                               | 94         |

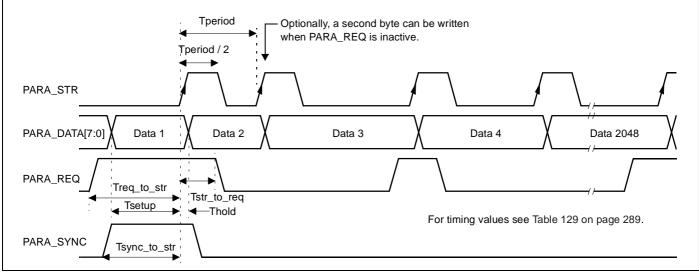

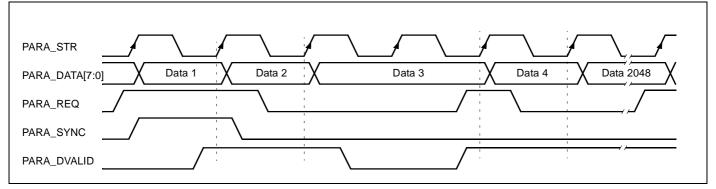

| 13.4             | Parallel interface                                   | 95         |

| 13.5             | ATAPI interface                                      | 97         |

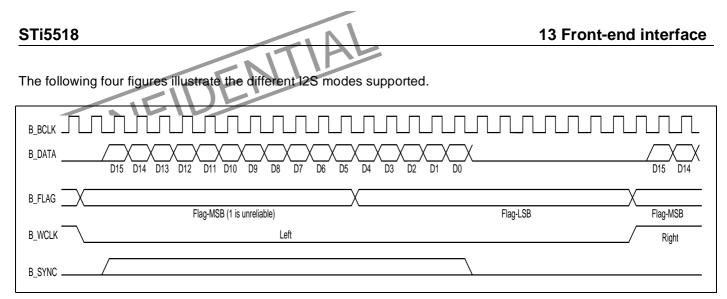

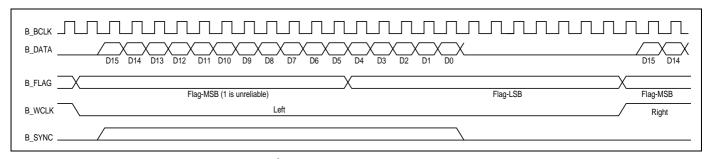

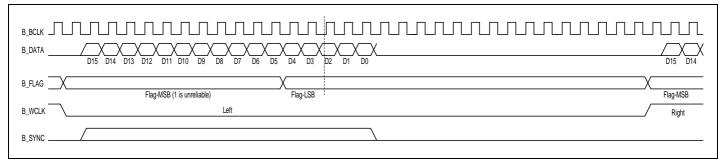

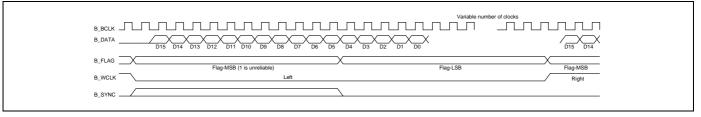

| 13.6             | I2S interface                                        | 98         |

| 13.7             | Decryption cell                                      | 104        |

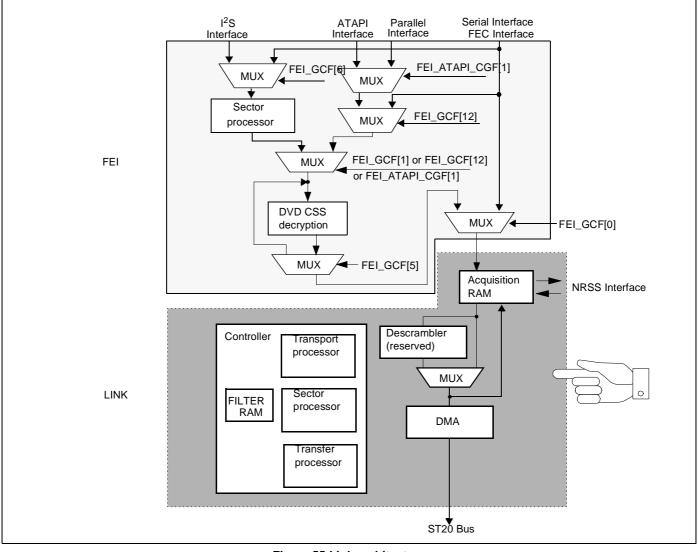

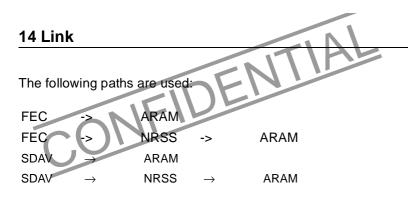

| 14               | Link                                                 |            |

| 14.1             | Introduction                                         | 105        |

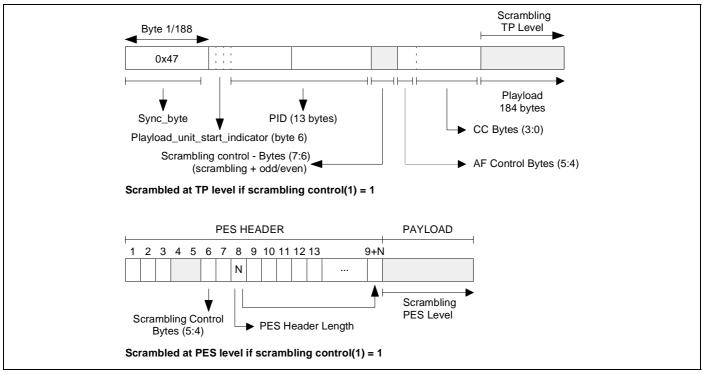

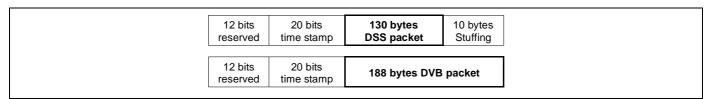

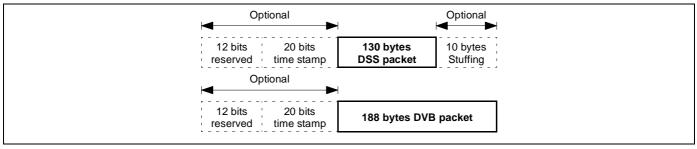

| 14.2             | MPEG-2 & DSS systems layers                          | 105        |

| 14.3             | Overview                                             |            |

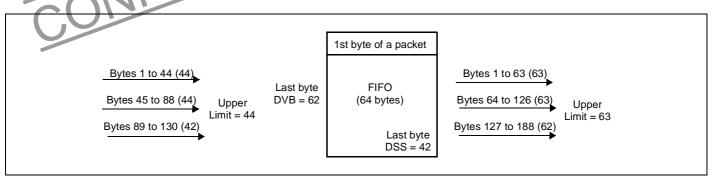

| 14.4             | Detailed description                                 | 109        |

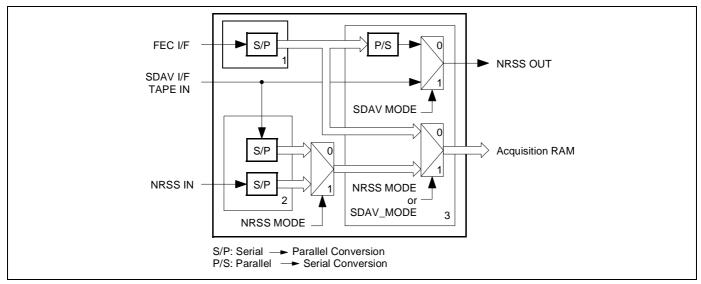

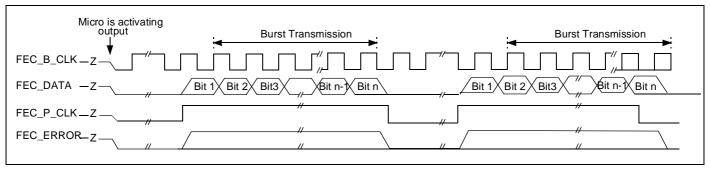

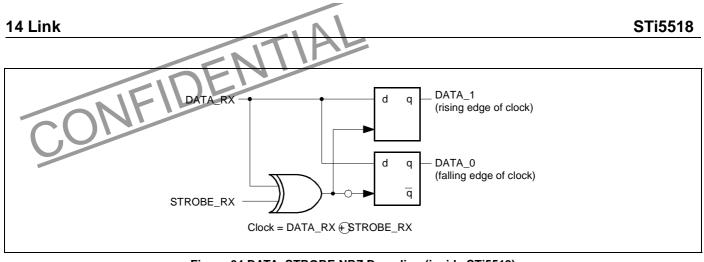

| 14.4.1           | Input interface                                      | 109        |

| 14.4.2           | NRSS interface                                       |            |

| 14.4.3<br>14.4.4 | Descrambler                                          |            |

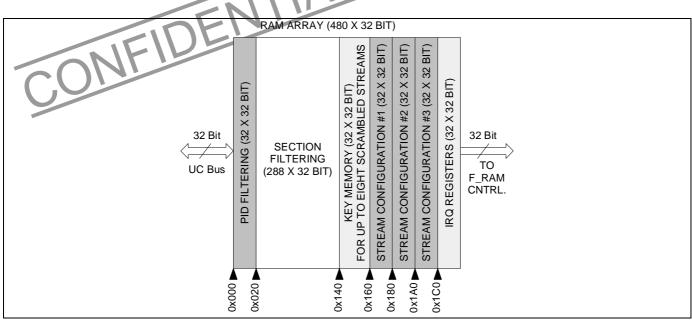

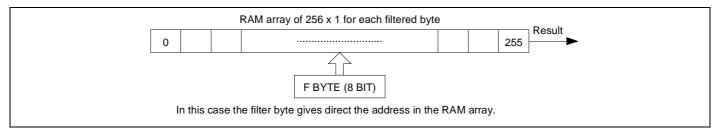

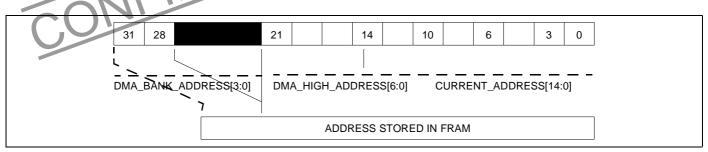

| 14.4.4           | FRAM                                                 |            |

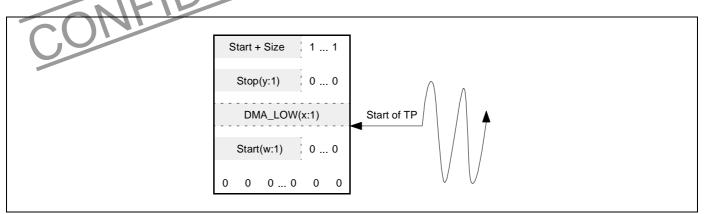

| 14.4.6           | DMA                                                  | 120        |

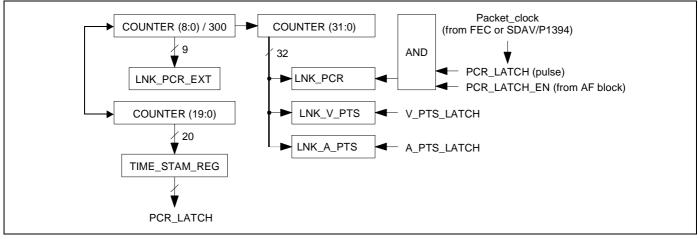

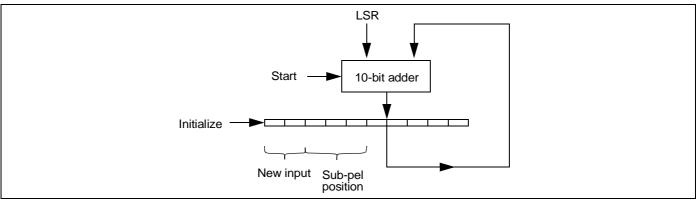

| 14.4.7           | Clock recovery                                       | 123        |

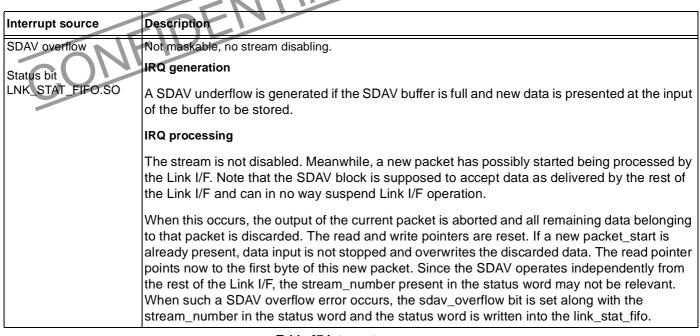

| 14.4.8           | Interrupts                                           |            |

| 14.5             | DVD/link data analyzer                               |            |

| 14.6             | Hard disk drive buffer control                       |            |

| 15               | MPEG video decoder                                   |            |

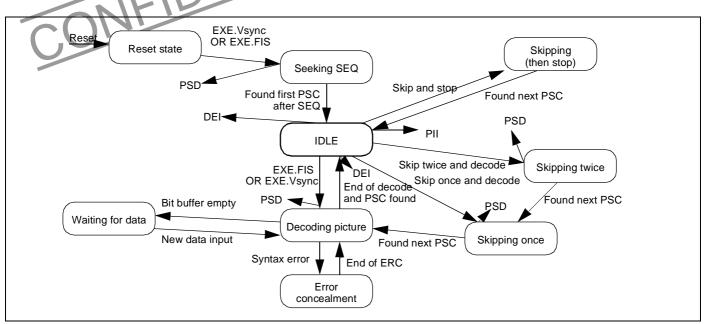

| 15.1             | Decoder operation                                    |            |

| 15.2             | Reset                                                | 133        |

| 15.3             | Bit buffer and start-code detection (video)          | 134        |

| 15.3.1           | Bit buffer                                           |            |

| 15.3.2           | Start code detection                                 | 134        |

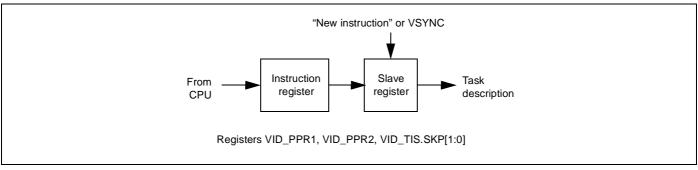

| 15.3.3           | Video decoding pipeline control                      |            |

| 15.4             | Quantization table loading                           |            |

| 15.5             | Memory mapping of data                               |            |

| 15.6             |                                                      |            |

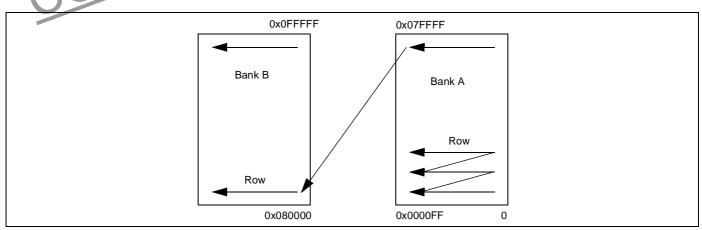

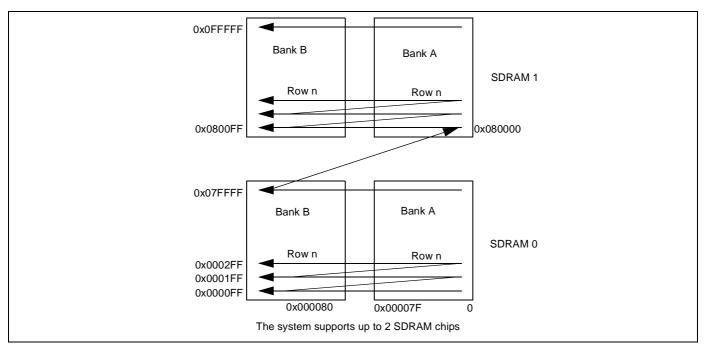

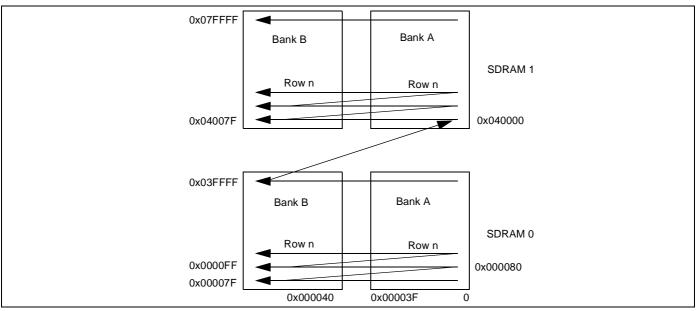

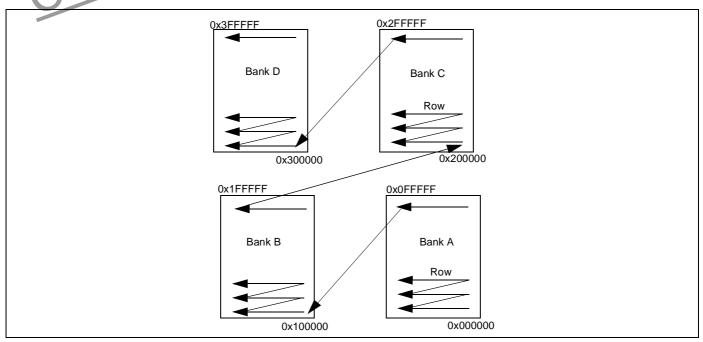

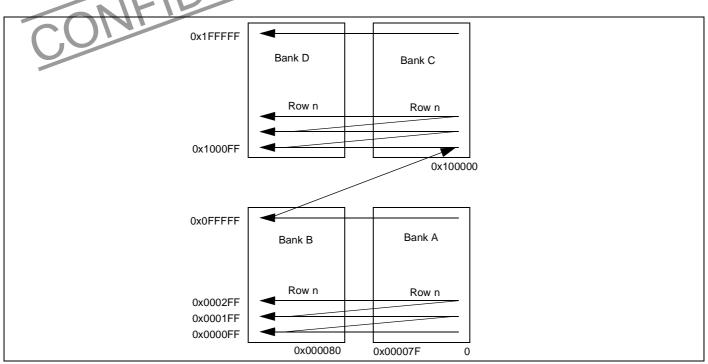

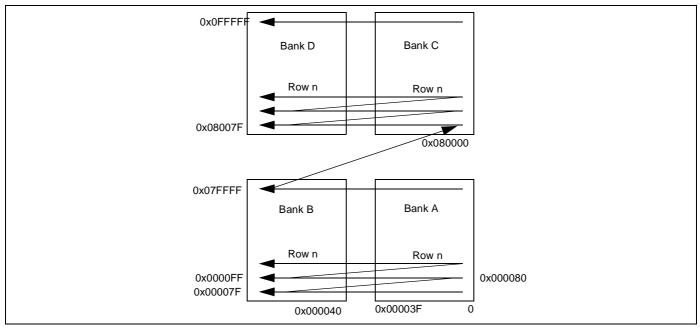

| 15.6.1<br>15.6.2 | Mapping 1 or 2 x 16-Mbit SDRAM                       | 138<br>140 |

| 15.6.3           | Memory segments                                      | 142        |

| 15.6.4           | Arrangement of pixel-pairs inside a luma SDRAM row   | 142        |

| 15.6.5           | Arrangement of pixel-pairs inside a chroma SDRAM row |            |

| 15.7             | Using picture pointers                               |            |

| 15.8             | Video pipeline                                       |            |

| 15.8.1           | Decoding task                                        | 144        |

| 15.8.2           | PES parser                                           |            |

| 15.9             | PES parser                                           |            |

| 15.10            | Ennanced trick-modes                                 | 148        |

| STi5518 | 3 |

|---------|---|

|---------|---|

| STi551             | 8                                                                       |

|--------------------|-------------------------------------------------------------------------|

|                    |                                                                         |

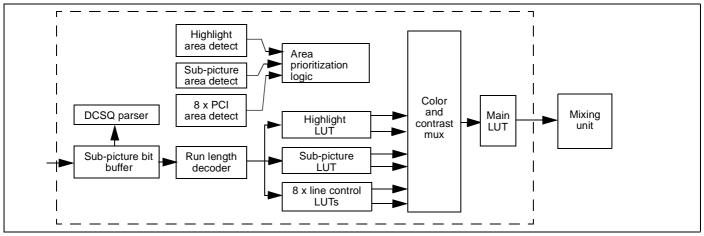

| 16                 | Sub-picture decoder                                                     |

| 16.1               | Introduction                                                            |

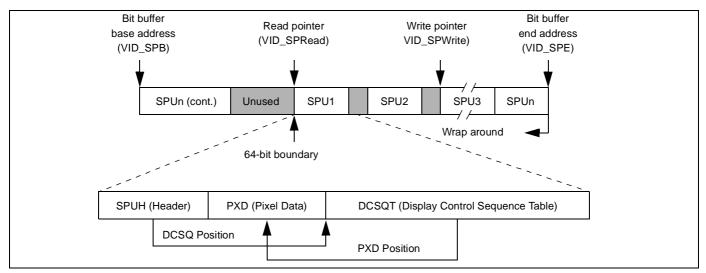

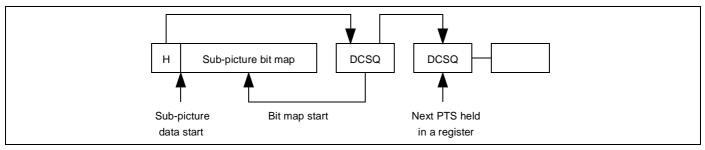

| 16.2               | Buffer management and pointers                                          |

| 16.3               | Operation                                                               |

| 16.4               | Sub-picture display                                                     |

| 16.4.1             | Look-up tables                                                          |

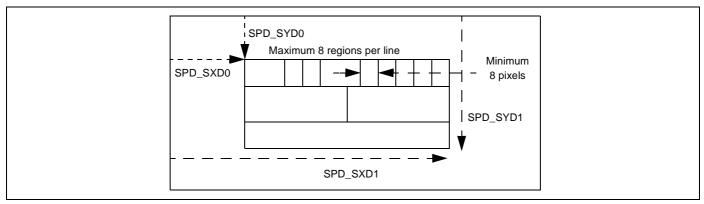

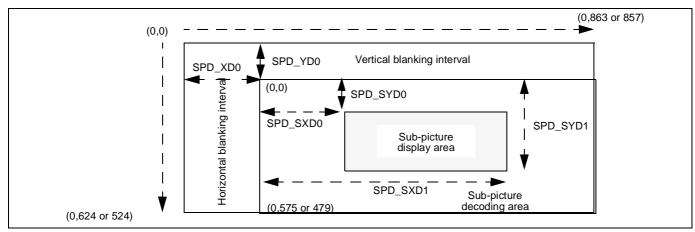

| 16.4.2             | Sub-picture areas                                                       |

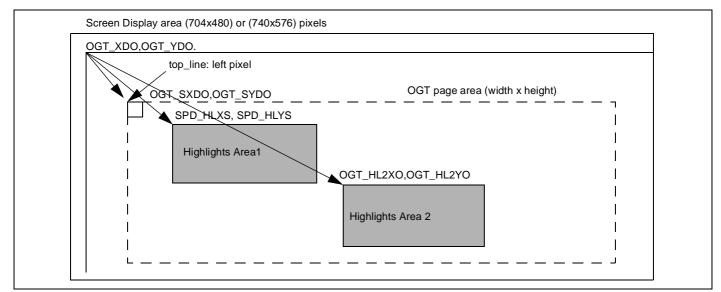

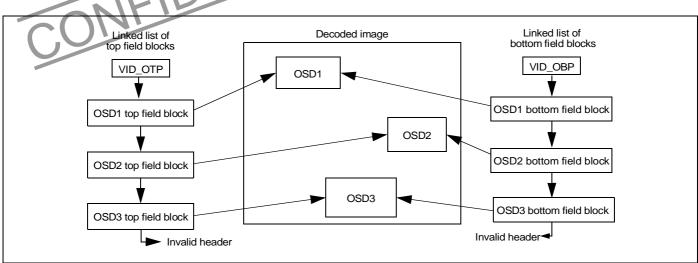

| 17                 | Overlay graphics and texts                                              |

| 17.1               | Introduction                                                            |

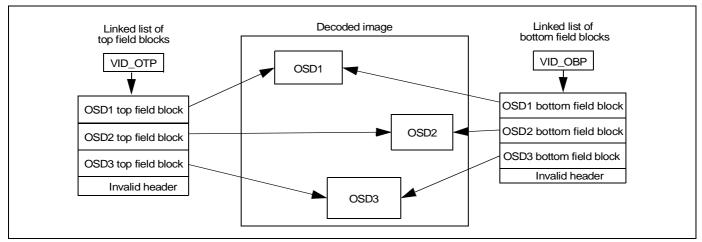

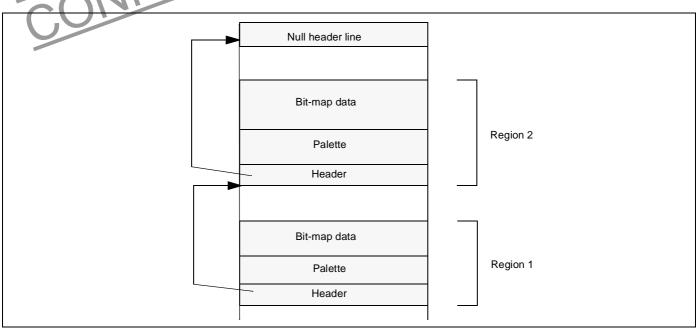

| 17.2               | Buffer management                                                       |

| 17.3               | Operation                                                               |

| 17.4               | Display                                                                 |

| 18                 | Display planes                                                          |

| 18.1               | Overview                                                                |

| 18.2               | Background color plane                                                  |

| 18.3               | MPEG video plane                                                        |

| 18.3.1             | Setting-up the display 158                                              |

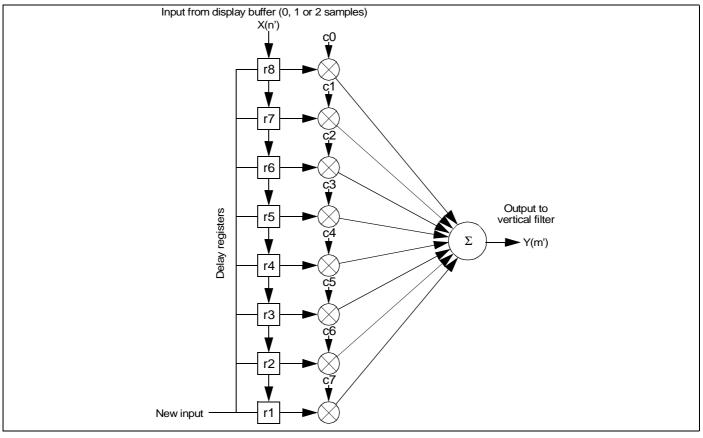

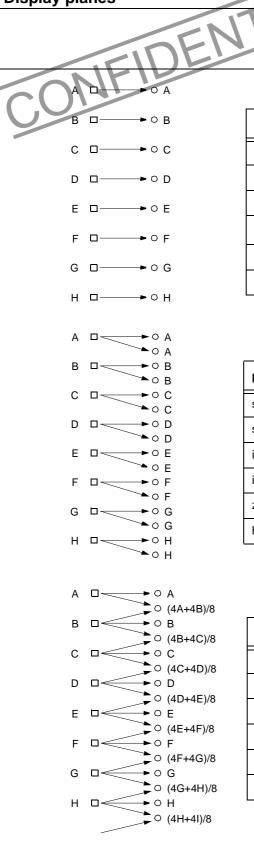

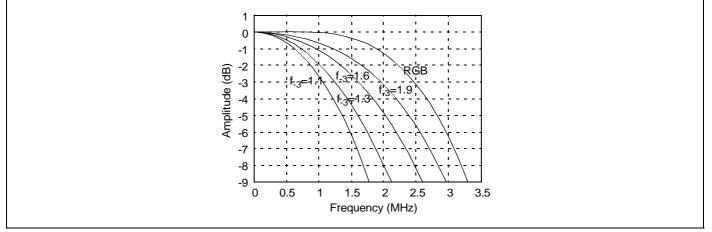

| 18.3.2<br>18.3.3   | Sample rate converter                                                   |

| 18.3.4             | Degradation mode                                                        |

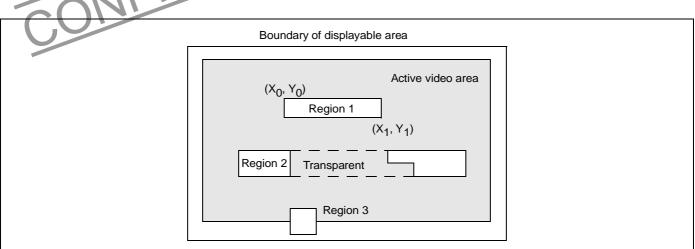

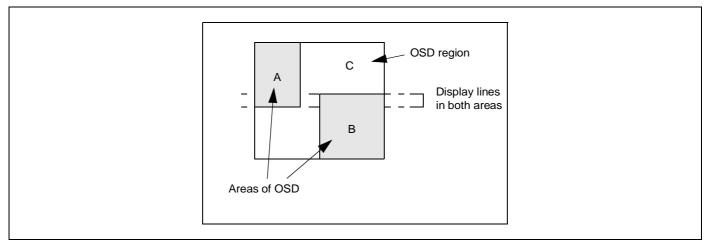

| 18.4               | On-screen display (OSD)                                                 |

| 18.4.1             | Using the OSD 170                                                       |

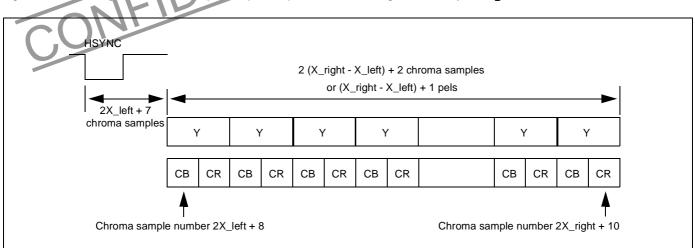

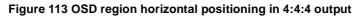

| 18.4.2             | OSD regions                                                             |

| 18.4.3<br>18.4.4   | OSD specification         171           OSD region position         173 |

| 18.4.5             | Color palette 174                                                       |

| 18.4.6<br>18.4.7   | OSD bit-map                                                             |

| 18.4.7             | OSD block header format                                                 |

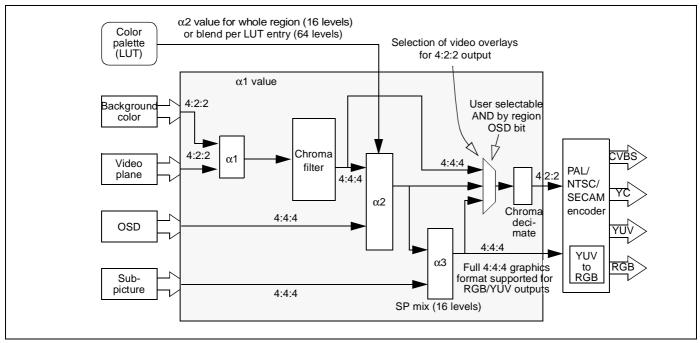

| 18.4.9             | Mixing OSD with video 181                                               |

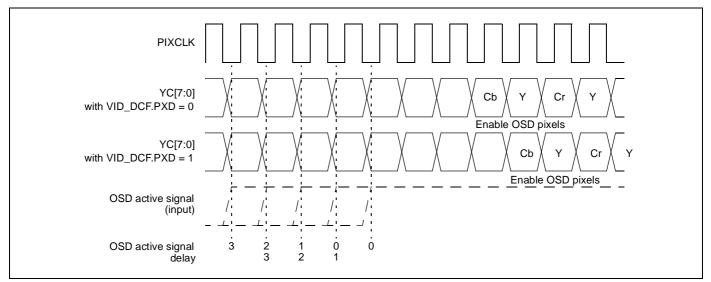

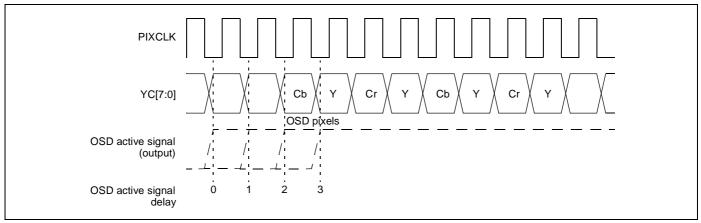

| 18.4.10<br>18.4.11 | Anti-flicker and anti-flutter filters 181<br>OSD active signal 182      |

| 18.5               | Sub-picture or cursor plane                                             |

| 18.6               | Mixing display planes                                                   |

| 18.6.1             | 4:2:2 Output control                                                    |

| 19                 | SDRAM block move                                                        |

|                    |                                                                         |

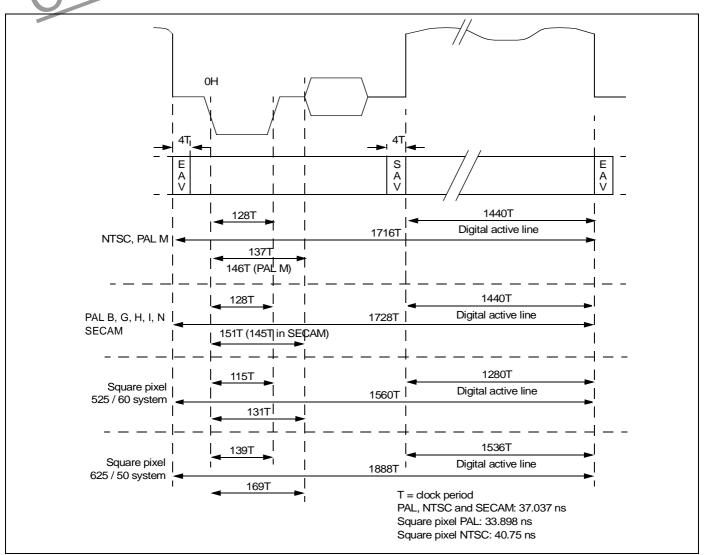

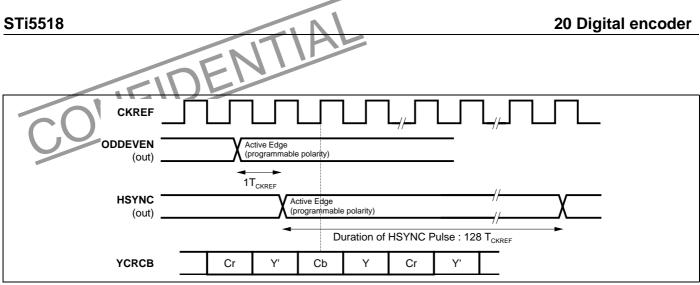

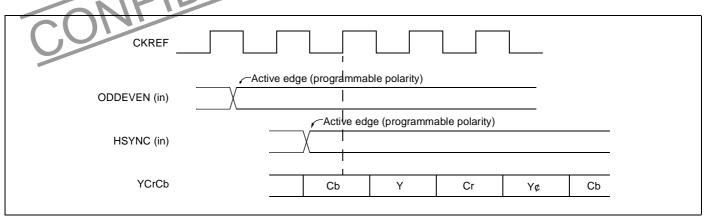

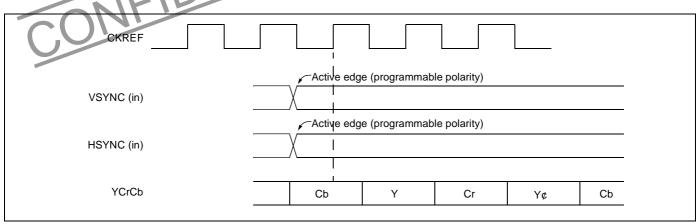

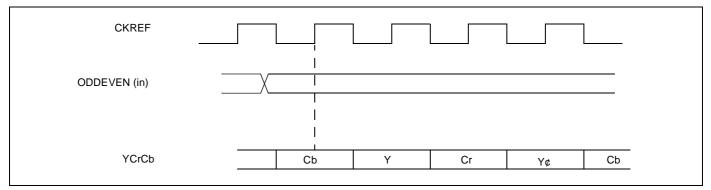

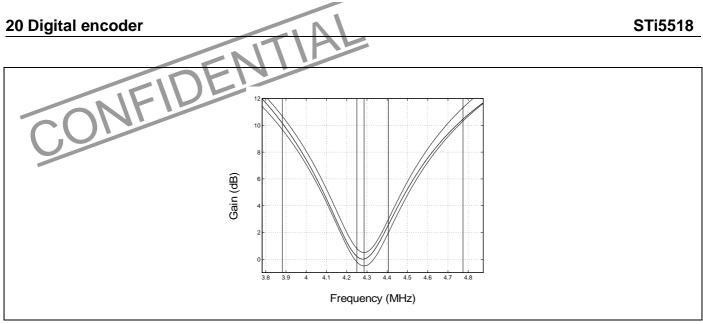

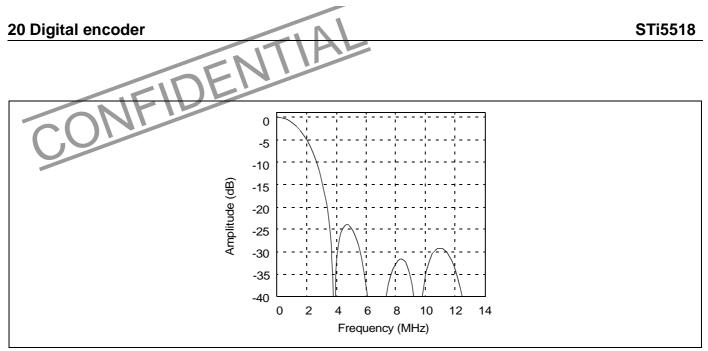

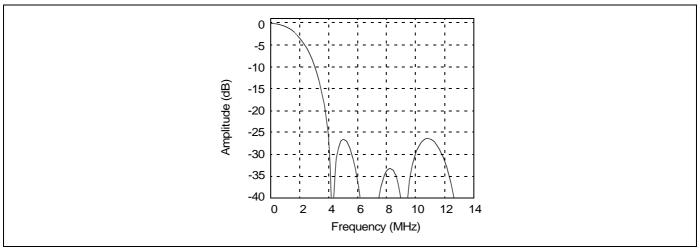

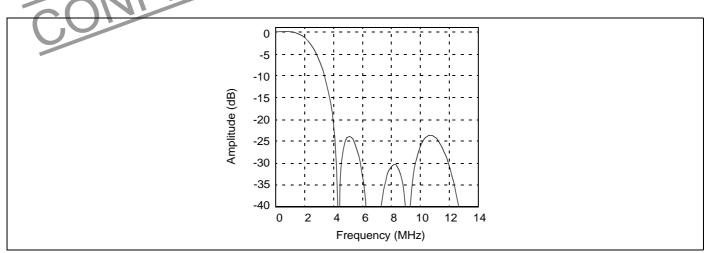

| 20                 | Digital encoder                                                         |

| 20.1               | Introduction                                                            |

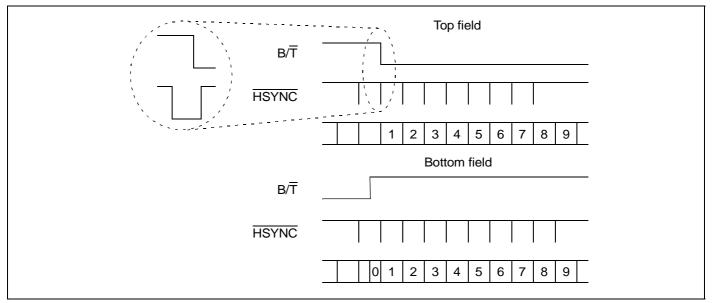

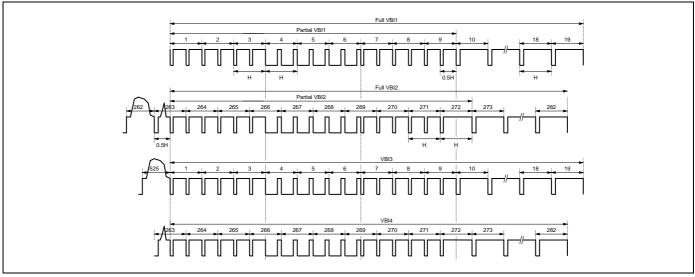

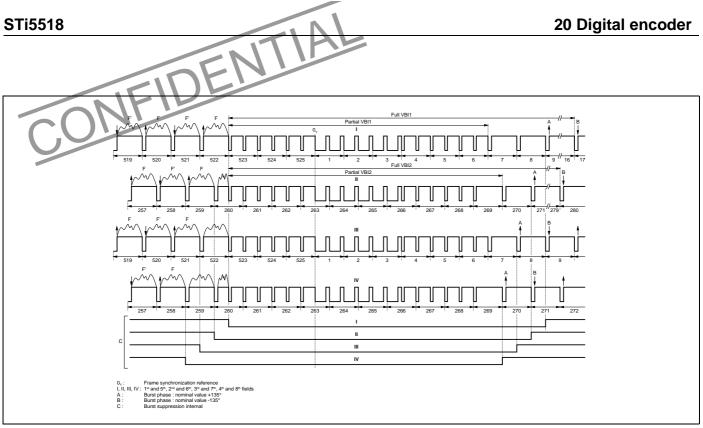

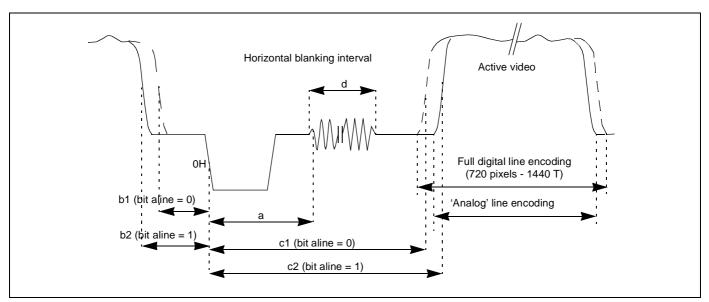

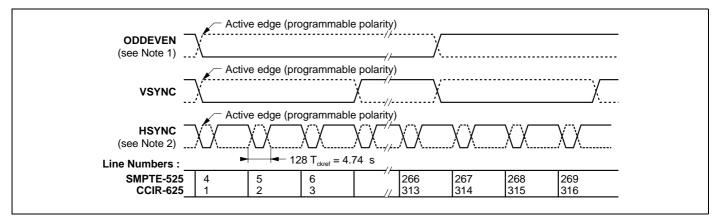

| 20.2               | Video timing                                                            |

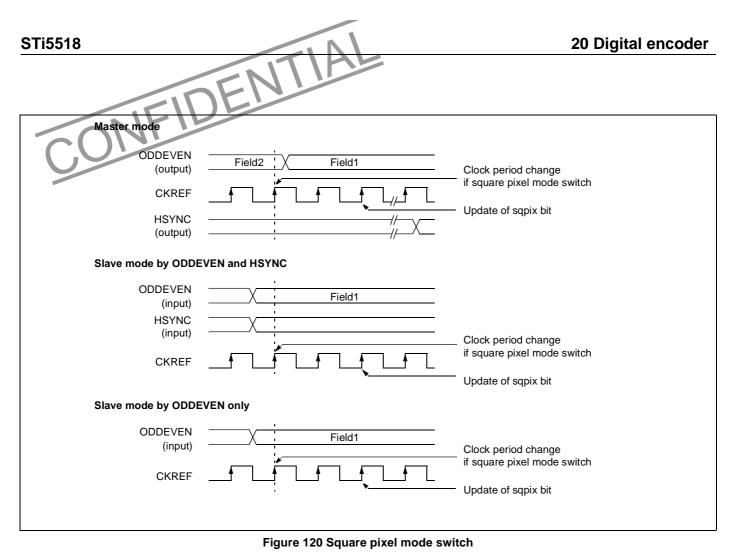

| 20.3               | Reset procedure                                                         |

| 20.4               | Master mode                                                             |

| 20.5               | Slave modes 193                                                         |

| 20.5.1<br>20.5.2   | Introduction 193<br>Line-based synchronization 193                      |

| 20.5.2 20.5.3      | Frame-based synchronization 194                                         |

| 20.5.4             | Sync-in-data based synchronization 196                                  |

| 20.6               | Input demultiplexor                                                     |

|         |                                           | STi5518    |

|---------|-------------------------------------------|------------|

|         |                                           | 5115510    |

| ~~ -    | Subcarrier generation                     | 100        |

| 20.7    |                                           | 199        |

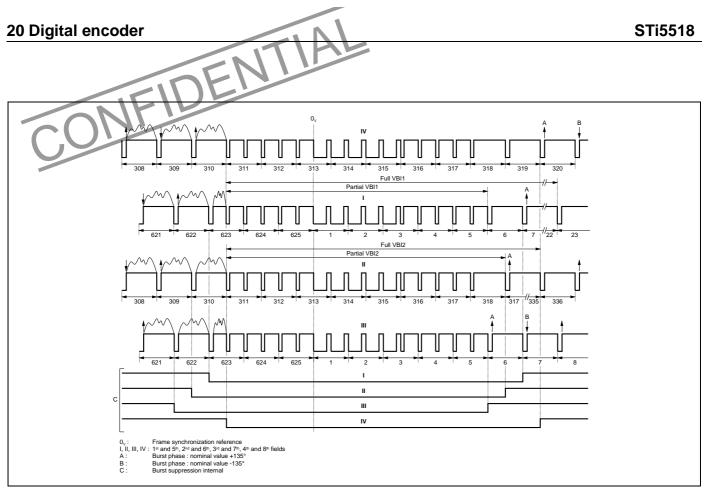

| 20.8    | Burst insertion (PAL and NTSC)            |            |

| 20.9    | Subcarrier insertion (SECAM)              |            |

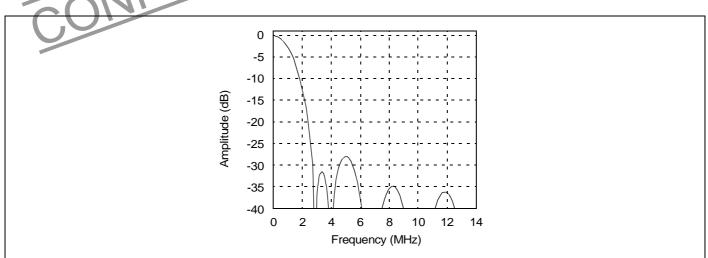

| 20.10   | Luminance encoding                        |            |

| 20.11   | Chrominance encoding                      |            |

| 20.12   | Composite video signal generation         |            |

| 20.13   | RGB and UV encoding                       |            |

| 20.14   | Closed-captioning                         |            |

| 20.15   | CGMS encoding                             |            |

| 20.16   | WSS encoding                              |            |

| 20.17   | VPS encoding                              |            |

| 20.18   | Teletext encoding                         |            |

| 20.19   | Line skip and line insert capability      | 212        |

| 20.20   | CVBS, S-VHS, RGB and UV outputs           | 212        |

| 21      | Teletext DMA                              | 214        |

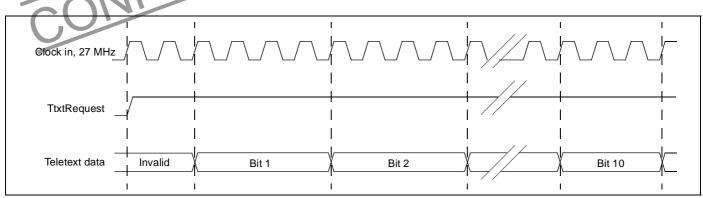

| 21.1    | Introduction                              | 214        |

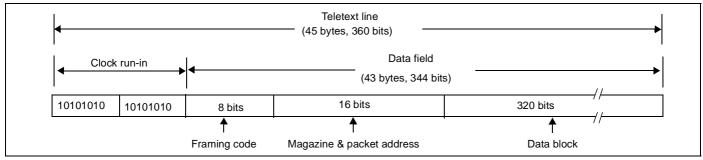

| 21.2    | Teletext packet format                    | 214        |

| 21.3    | Data transfer sequence                    | 214        |

| 21.4    | Interrupt control                         | 215        |

| 21.5    | Teletext registers                        |            |

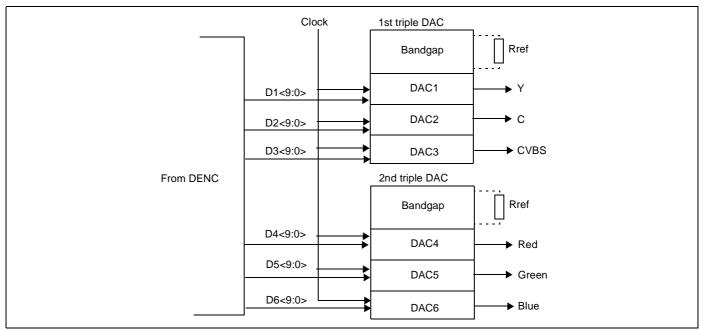

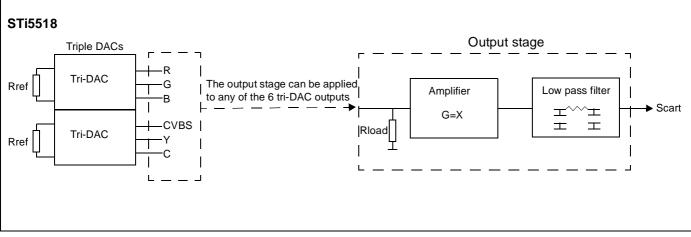

| 22      | Double triple video DAC                   | 216        |

| 22.1    | Description                               |            |

| 22.2    | Input codes for video application         |            |

| 22.3    | Video output voltage level                |            |

| 22.4    | Video specifications and DAC setup        |            |

| 22.5    | Output-stage adaptation and amplification |            |

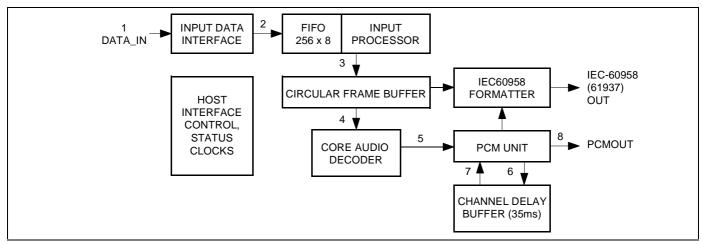

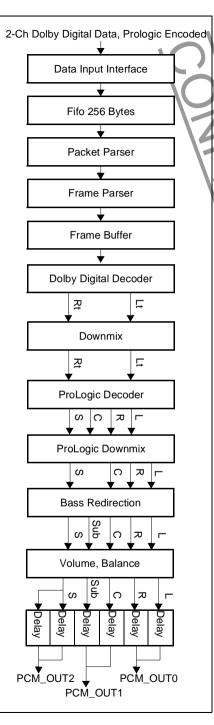

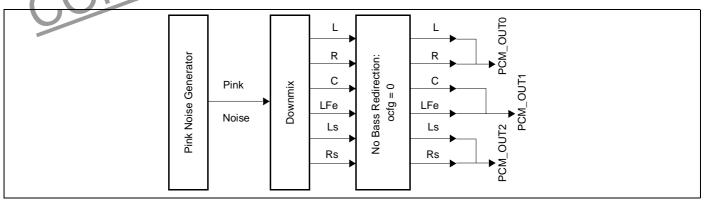

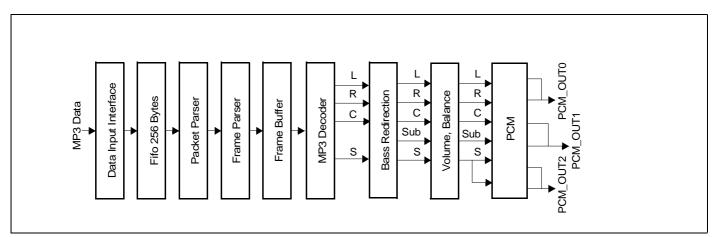

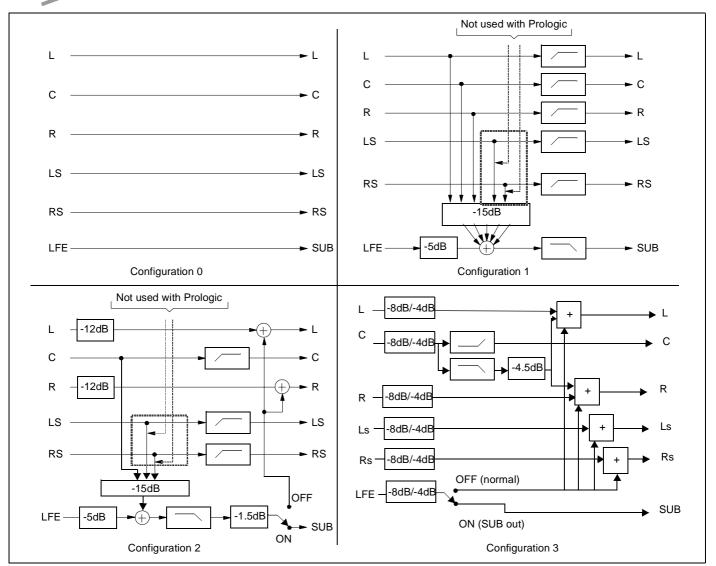

| 23      | Audio decoder                             | 219        |

| 23.1    | Features                                  |            |

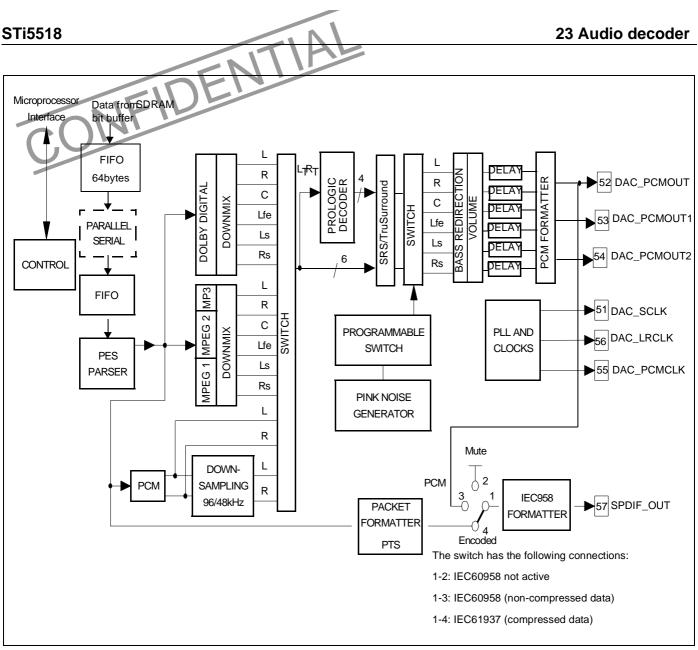

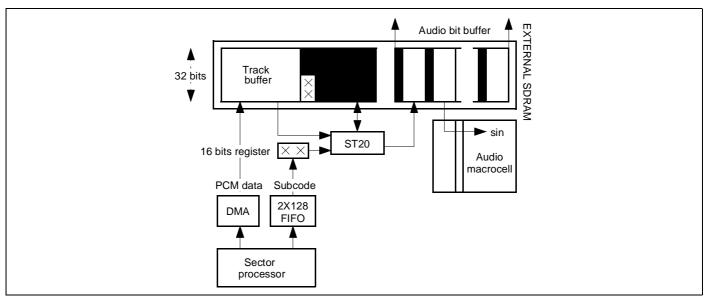

| 23.2    | Architecture overview                     |            |

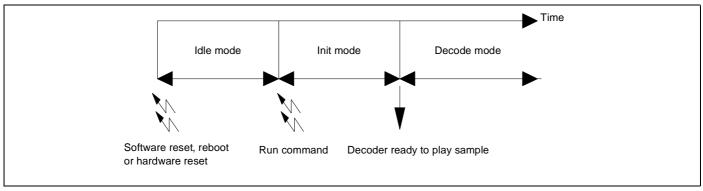

| 23.3    | Decoding process                          |            |

| 23.4    | Operation                                 |            |

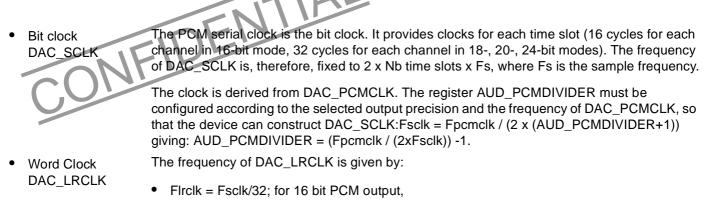

| 23.5    | Decoding states                           |            |

| 23.6    | Stream parsers                            |            |

| 23.7    | Decoding modes                            |            |

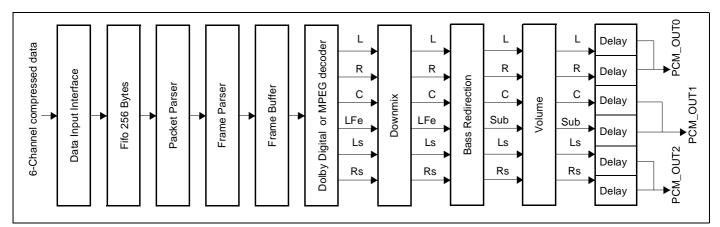

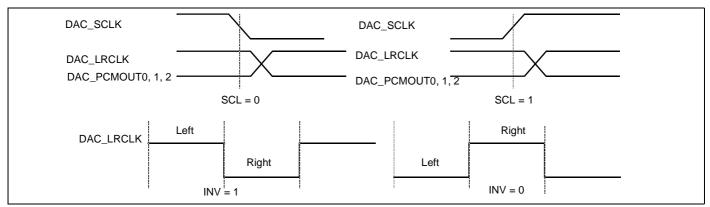

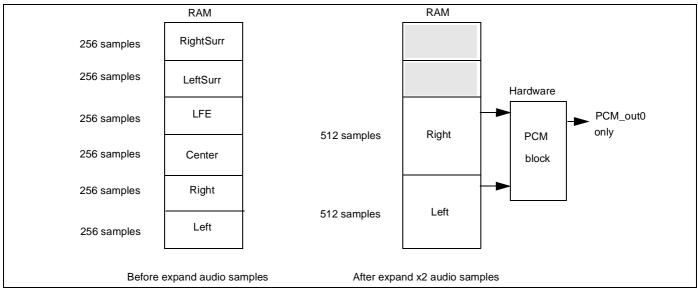

| 23.8    | PCM output                                |            |

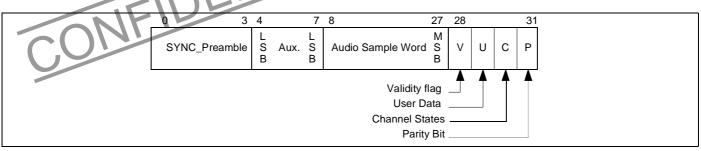

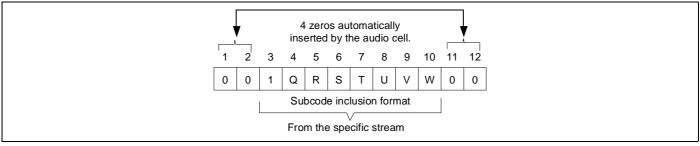

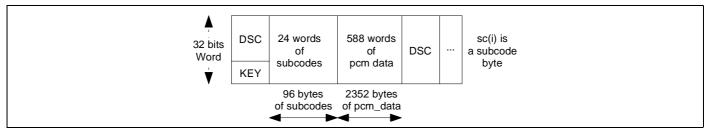

| 23.9    | SPDIF output                              |            |

| 23.10   | Interrupts                                |            |

| 23.10   | Audio/video synchronization               |            |

| 23.11   | PCM beep tone                             |            |

| 23.12   | Audio trick modes                         |            |

| 23.13   |                                           |            |

| 23.13.1 | Slow forward                              | 238<br>238 |

| 23.13.3 | Fast forward                              | 239        |

| 23.13.4 | SPDIF output for audio trick modes        | 240        |

| STi551           | 8                                                                                |

|------------------|----------------------------------------------------------------------------------|

|                  |                                                                                  |

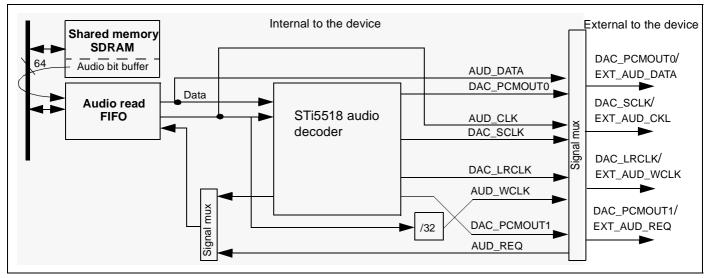

| 24               | External audio decoder interface 241                                             |

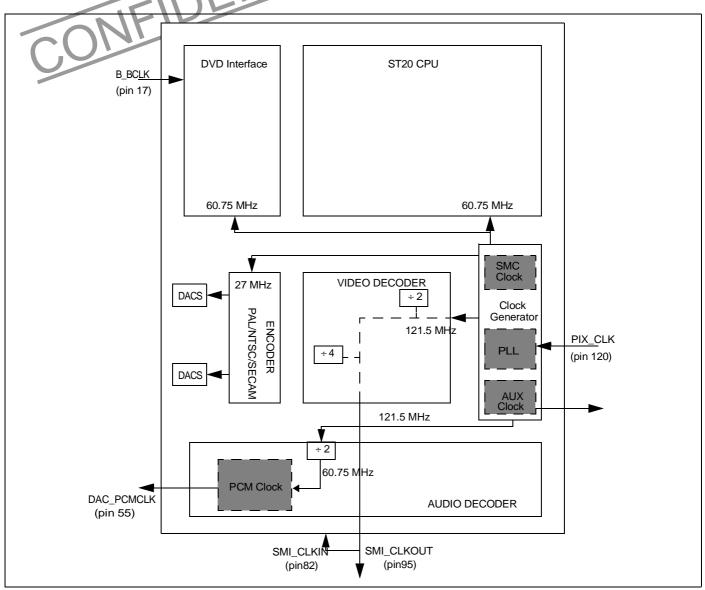

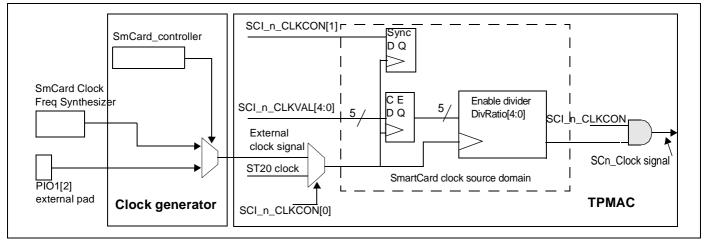

| 25               | Clock generator                                                                  |

| 25.1             | Introduction 242                                                                 |

| 25.2             | System clocks                                                                    |

| 25.3             | PCM clock                                                                        |

| 25.4             | SmartCard clocks                                                                 |

| 25.5             | Auxiliary clock                                                                  |

| 25.6             | Low-power, watchdog and power-down                                               |

|                  |                                                                                  |

| 26               | MPEGDMA controller                                                               |

| 27               | Block move DMA                                                                   |

| 28               | PWM and counter module                                                           |

| 28.1             | External interface                                                               |

| 28.2             | PWM outputs                                                                      |

| 28.3             | Capture inputs                                                                   |

| 28.4             | Compare (programmable timer) facilities                                          |

| 28.5             | Capture/compare counter, prescaling and clocking                                 |

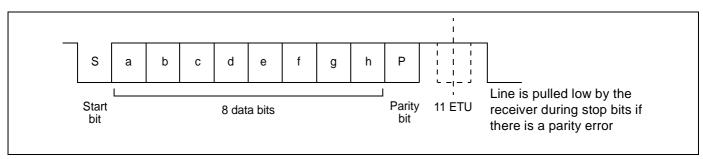

| 29               | Smartcard interface                                                              |

| 29.1             | External interface                                                               |

| 29.2             | SmartCard clock generator                                                        |

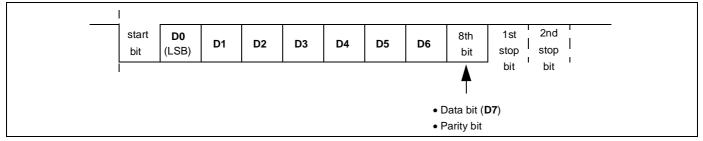

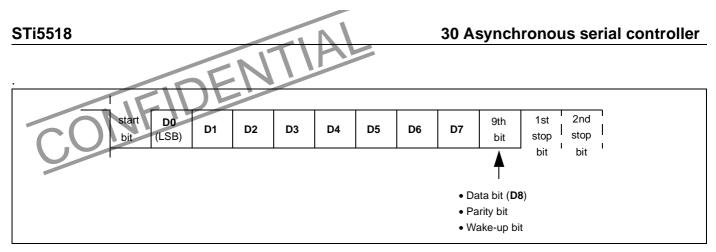

| 30               | Asynchronous serial controller                                                   |

| 30.1             | Control                                                                          |

| 30.1.1           | Resetting the FIFOs 253                                                          |

| 30.1.2           | Transmission and reception 253                                                   |

| 30.2             | Data frames                                                                      |

| 30.2.1<br>30.2.2 | 8-bit data frames 254<br>9-bit data frames 254                                   |

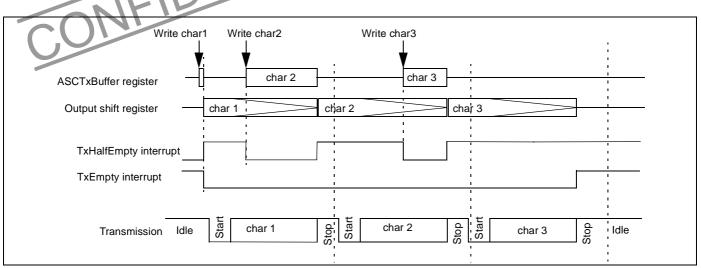

| 30.3             | Transmission                                                                     |

| 30.3.1           | Transmission with FIFOs enabled 255                                              |

| 30.3.2           | Double-buffered transmission 256                                                 |

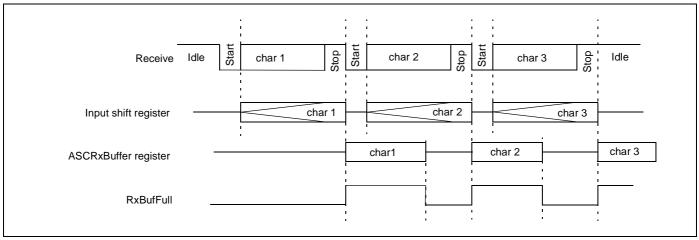

| 30.4             | Reception                                                                        |

| 30.4.1           | Hardware error detection 256                                                     |

| 30.4.2<br>30.4.3 | Input buffering modes 257<br>Time-out mechanism 258                              |

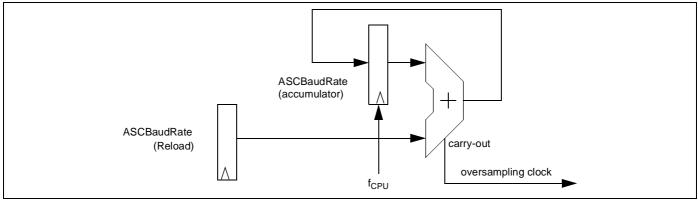

| 30.5             | Baud rate generation                                                             |

| 30.5.1           | Baud rates 258                                                                   |

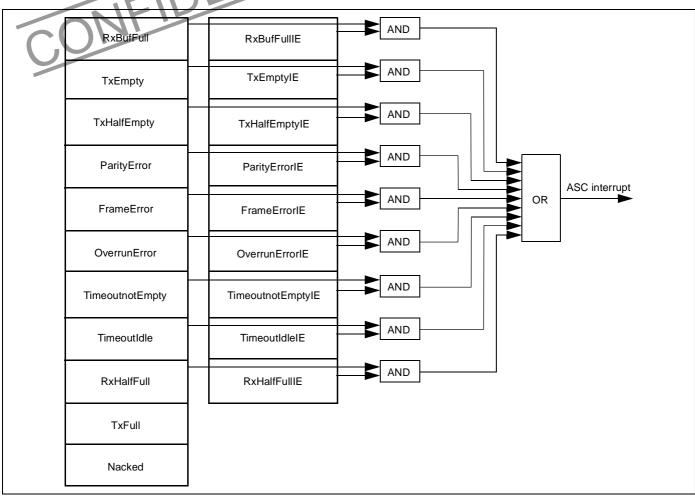

| 30.6             | Interrupt control                                                                |

| 30.6.1           | Using the ASC interrupts when FIFOs are disabled (double-buffered operation) 260 |

| 30.6.2           | Using the ASC interrupts when FIFOs are enabled 261                              |

| 30.7             | SmartCard operation                                                              |

| 30.7.1           | Control registers 262                                                            |

| 30.7.2<br>30.7.3 | Transmission                                                                     |

| 30.7.4           | Divergence from ISO SmartCard specification 264                                  |

|                  |                                                 | STi5518 |

|------------------|-------------------------------------------------|---------|

|                  |                                                 |         |

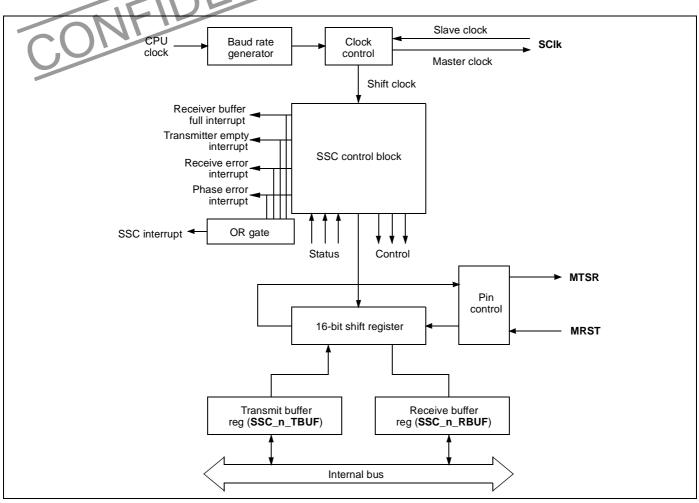

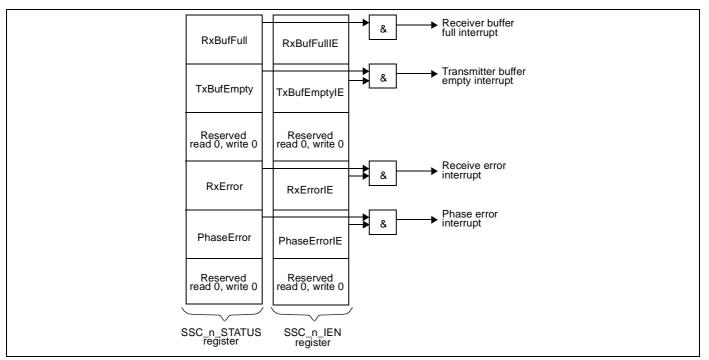

| 31               | Synchronous serial controller                   | 265     |

| 31.1             | Introduction                                    | 265     |

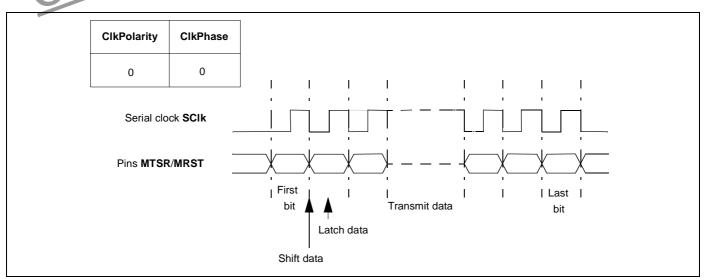

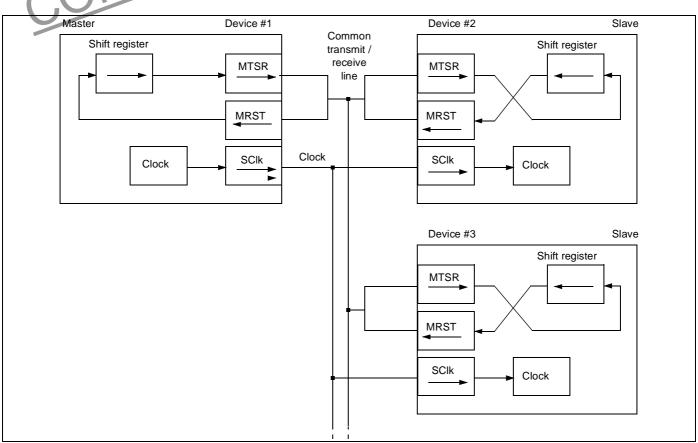

| 31.2             | Synchronous serial channel operation            |         |

| 31.3             | SSC clocking                                    |         |

| 31.4             | Half-duplex operation                           |         |

| 31.5             | Continuous transfers                            |         |

| 31.6             | Baud rates                                      |         |

| 31.7             | Hardware error detection capabilities           |         |

| 31.8             | Interrupt control                               |         |

| 31.9             | I2C hardware configuration                      | 271     |

| 32               | Parallel input/output port                      | 272     |

| 33               | Modem analog front-end interface -------------- |         |

| 33.1             | Overview                                        |         |

| 33.2             | Using the MAFEIF to connect to a modem          | 273     |

| 33.3             | Software                                        | 274     |

| 33.3.1           | Data exchange                                   |         |

| 33.3.2           | Control/status exchange                         |         |

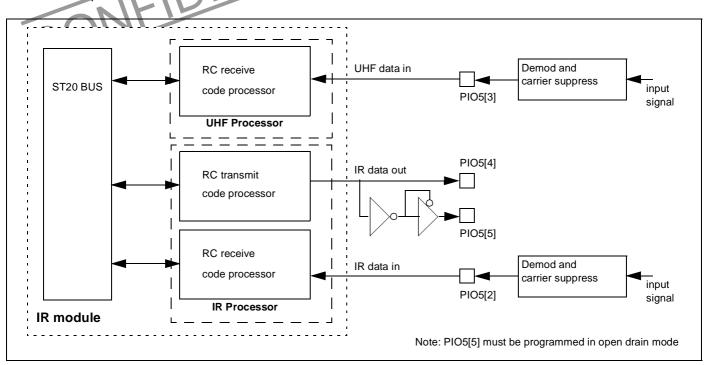

| 34               | Infrared transmitter/receiver                   |         |

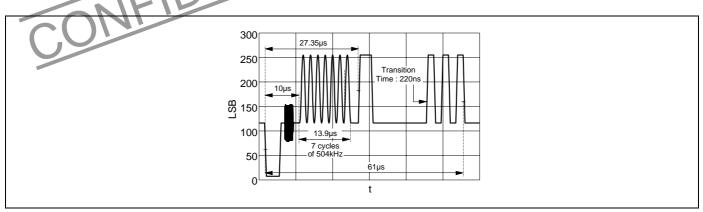

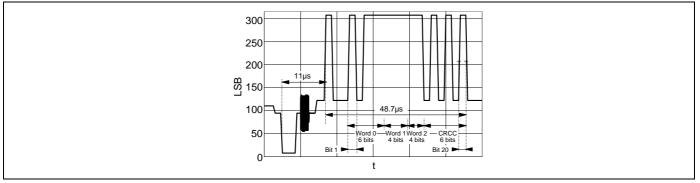

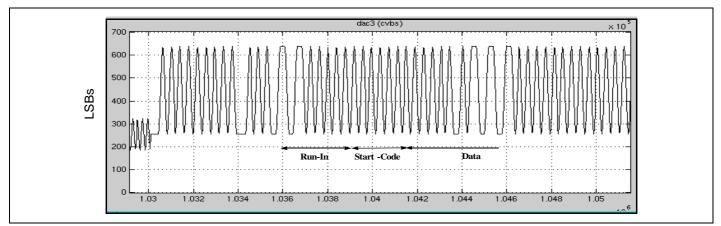

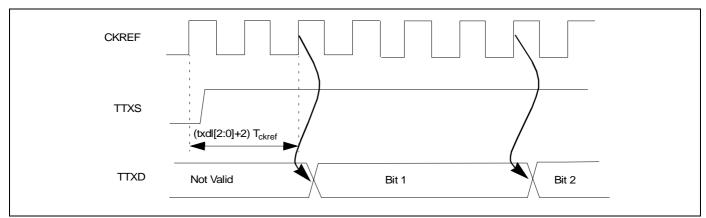

| 34.1             | Introduction                                    |         |

| 34.2             | Functional description                          | 275     |

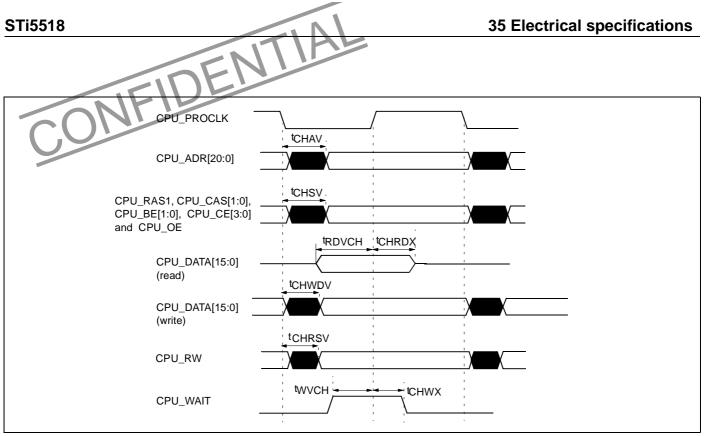

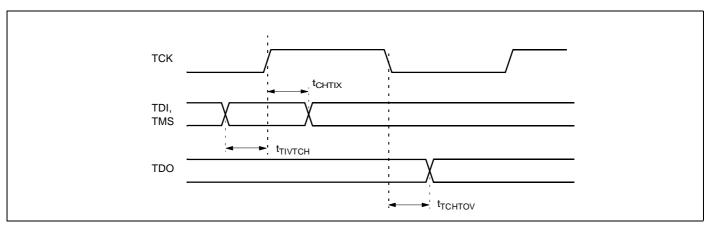

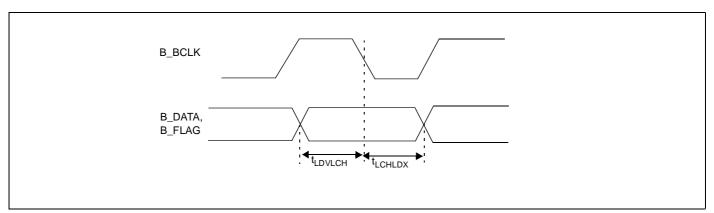

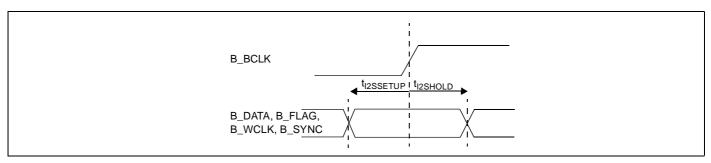

| 35               | Electrical specifications                       |         |

| 35.1             | Absolute maximum ratings                        |         |

| 35.2             | DC electrical characteristics                   |         |

| 35.2.1           | Static                                          |         |

| 35.2.2<br>35.2.3 | ST20 running at 60.75 MHz                       |         |

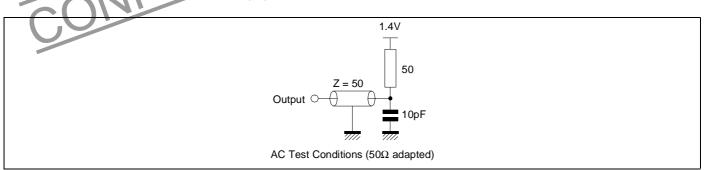

| 35.3             | AC test conditions                              |         |

| 35.4             | Operating conditions                            |         |

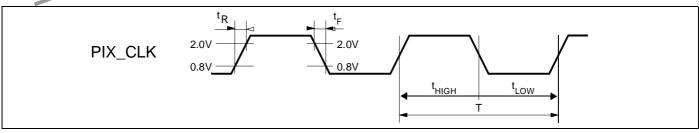

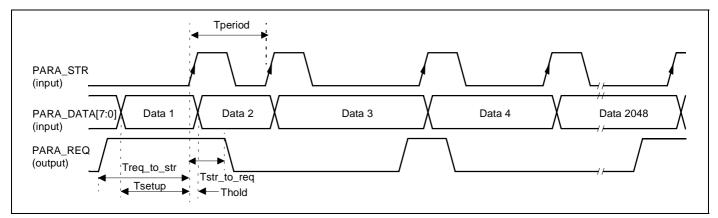

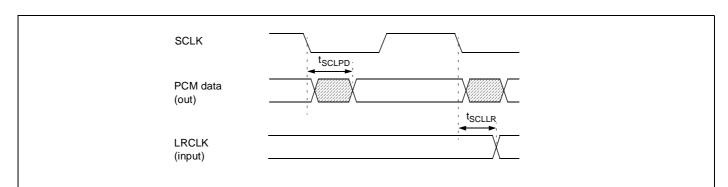

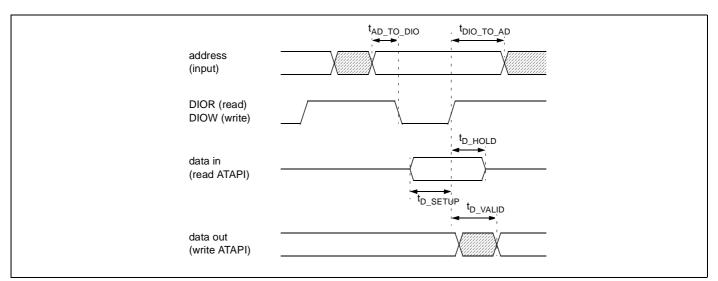

| 35.5             | Timing diagrams for IO interfaces               |         |

| 35.5.1           |                                                 |         |

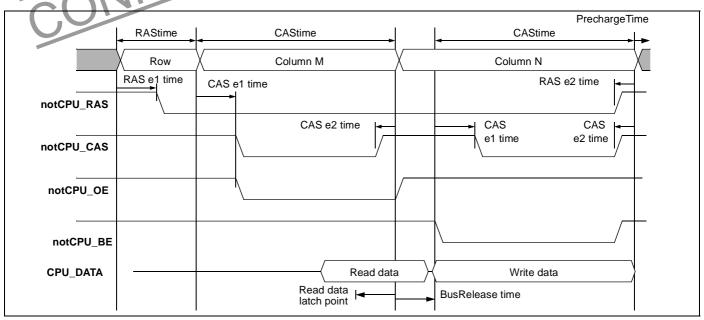

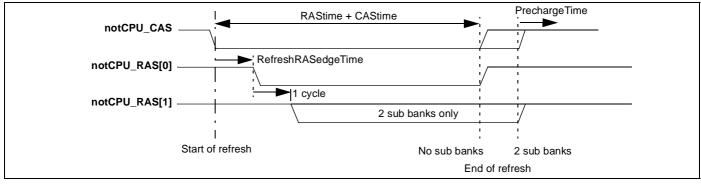

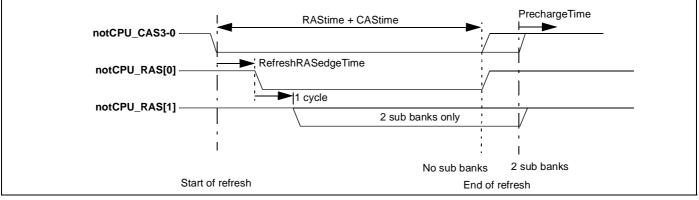

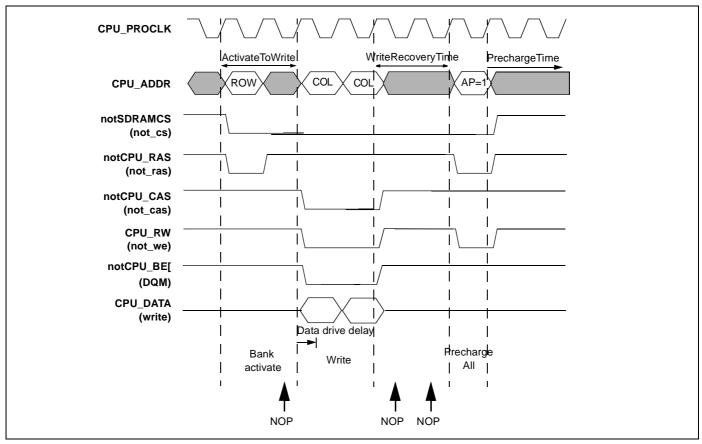

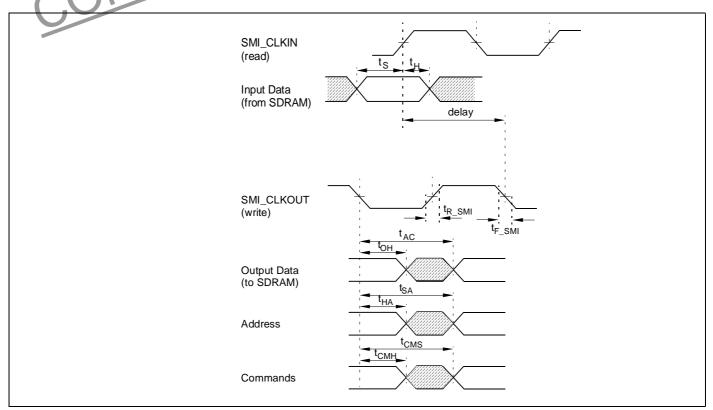

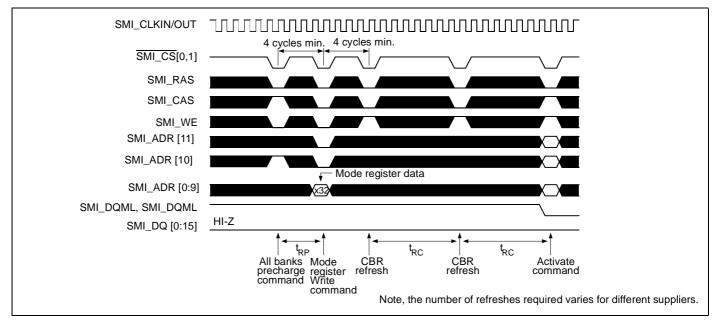

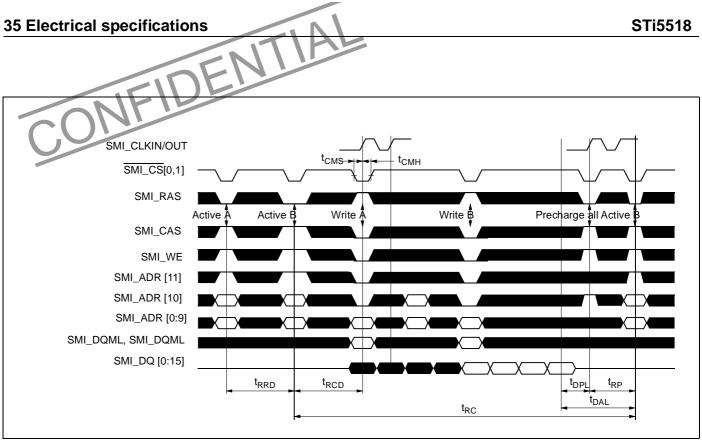

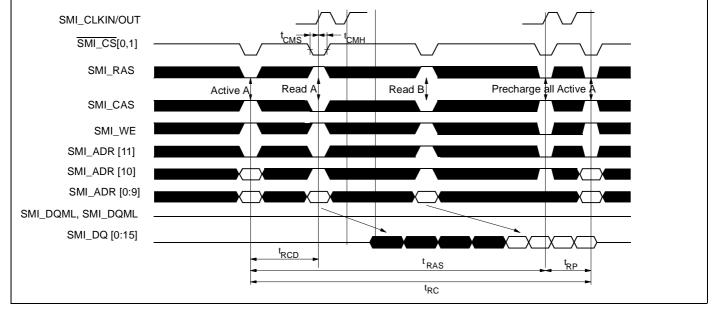

| 35.5.2           | SMI interface                                   | 282     |

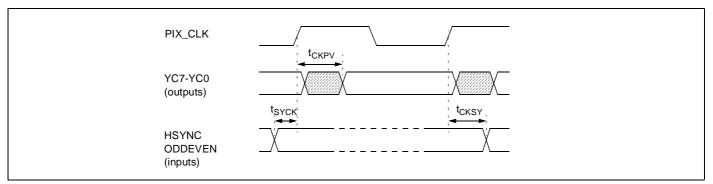

| 35.5.3           |                                                 |         |

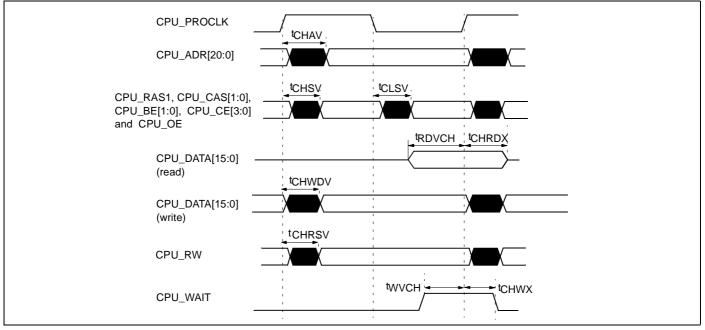

| 35.5.4<br>35.5.5 | EMI interface                                   |         |

| 35.5.6           | Link interface                                  | 288     |

| 35.5.7           | I2S interface                                   |         |

| 35.5.8<br>35.5.9 | Parallel interface                              |         |

| 35.5.10          | ATAPI interface                                 |         |

| 36               | Package mechanical data                         | 291     |

| 37               | Revision history                                |         |

| 37.1             | Changes for rev D                               |         |

| 37.2             | Changes for rev C                               | 292     |

| 37.3             | Changes for rev B                               | 292     |

**S**

# 1 Architecture overview

# 1.1 Introduction

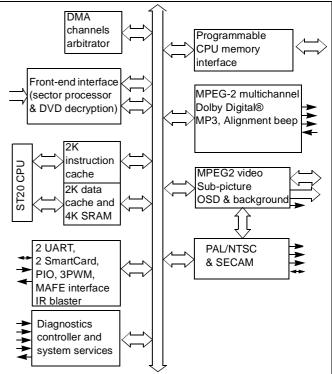

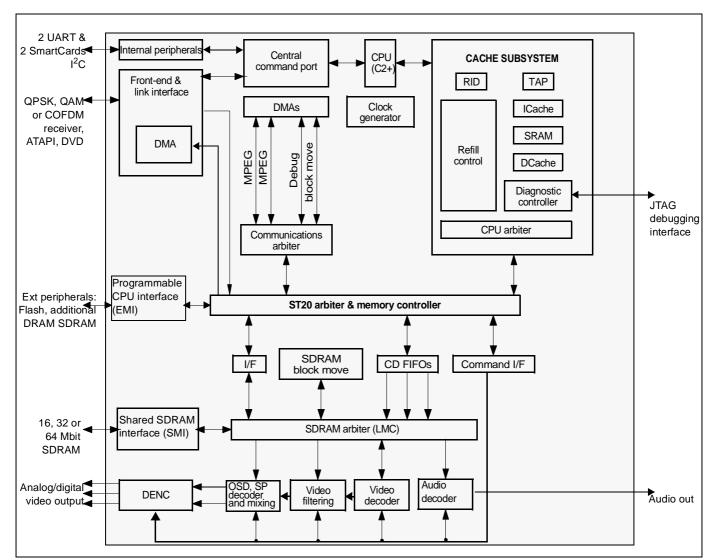

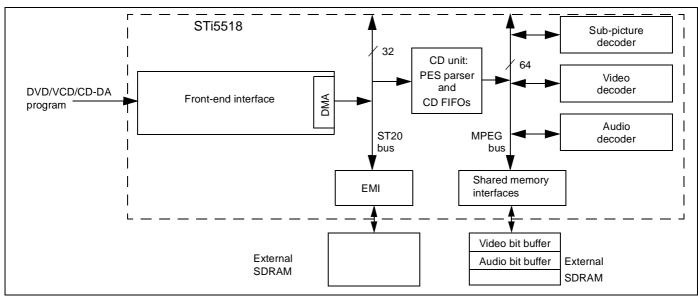

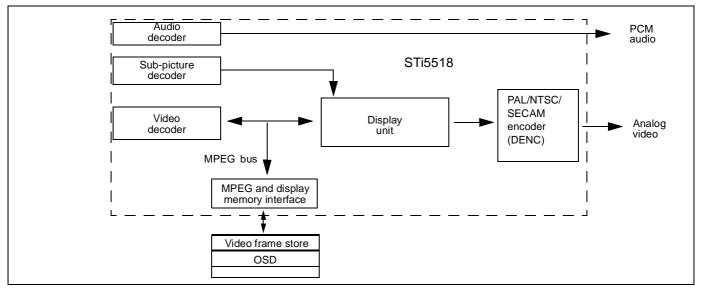

The figure below shows the architecture of the STi5518.

This chapter gives a brief overview of each of the functional blocks of the STi5518.

Figure 1 Functional block diagram

### **1** Architecture overview

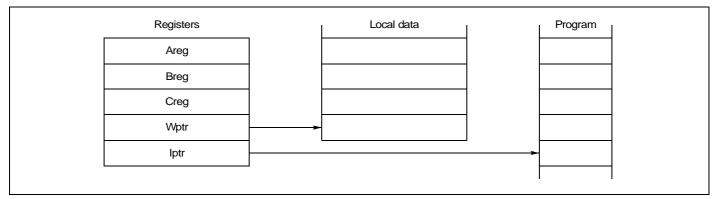

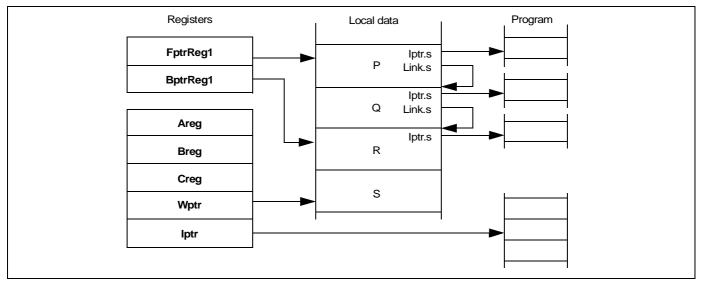

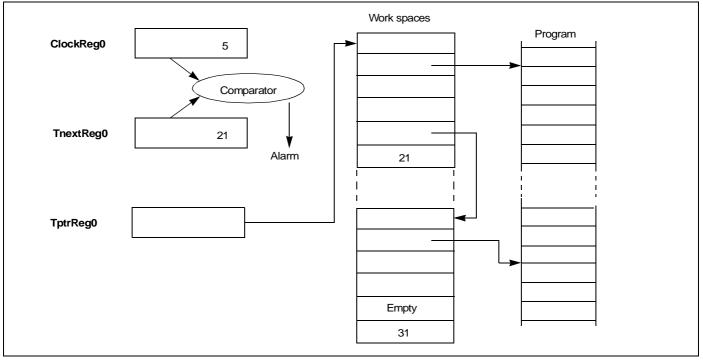

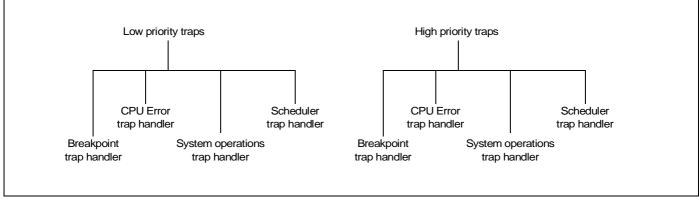

# 1.2 Central processor

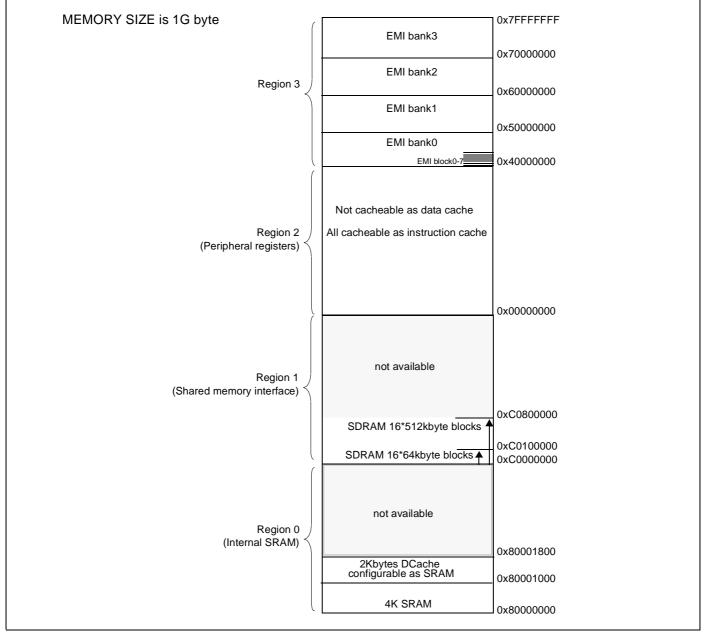

The STI5518 Central Processing Unit is a ST20C2+ 32-bit processor core. It contains instruction processing logic, instruction and data pointers, and an operand register. It directly accesses the high-speed on-chip SRAM, which can store data or programs and uses the cache to reduce access time to off-chip program and data memory.

The processor can access memory via the Programmable CPU Interface (often referred to as the EMI) or the Shared Memory Interface (SMI), which is shared with the video, audio, sub-picture and OSD decoders.

# 1.3 MPEG video decoder

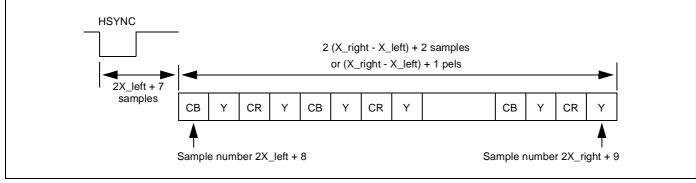

This is a real-time video compression processor supporting the MPEG-1 and MPEG-2 standards at video rates up to 720 x 480 x 60 Hz and 720 x 576 x 50 Hz. Picture format conversion for display is performed by vertical and horizontal filters. User-defined bitmaps can be super-imposed on the display picture by using the on-screen display function.

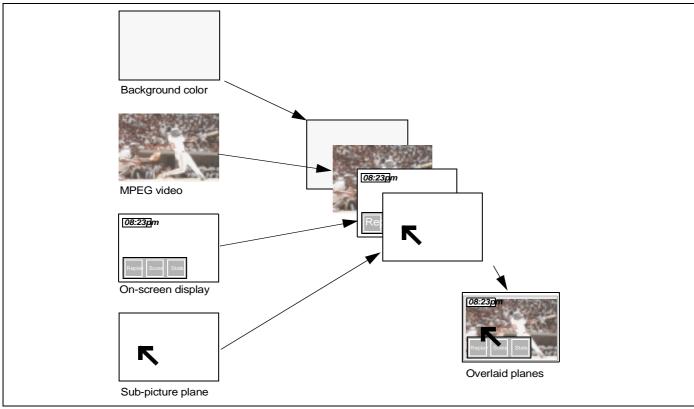

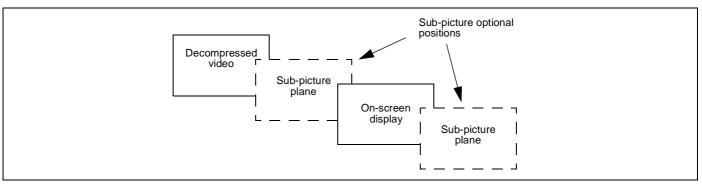

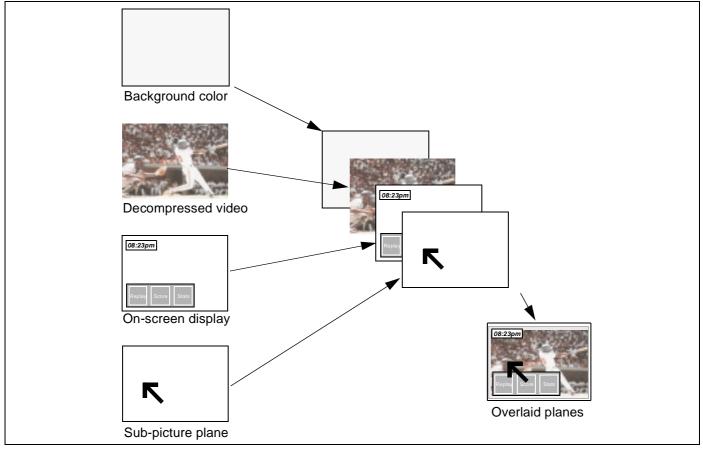

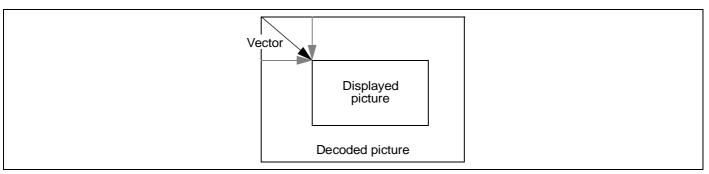

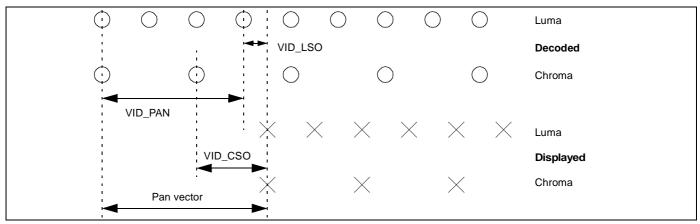

The display unit is part of the MPEG video decoder, it overlays the four display planes shown in the figure below. The display planes are normally overlaid in the order illustrated, with the background color at the back and the sub-picture at the front (used as a cursor plane). The sub-picture plane can alternatively be positioned between the OSD and MPEG video planes where it can be used as a second on-screen display plane.

Figure 2 Display planes

# 1.4 Audio decoder

The audio decoder accepts: Dolby Digital, MPEG-1 layers I, II and III, MPEG-2 layer II 6-channel, PCM, CDDA data formats; MPEG2 PES streams for MPEG-2, MPEG-1, Dolby Digital, MP3, and Linear PCM (LPCM). The audio decoder supports DTS® digital out (DVD DTS and CDDA DTS).

N

SPDIF input data (IEC-60958 or IEC-61937 standards) is accepted if an external circuitry extracts the PCM clock from the stream.

Skip frame, repeat blocks and soft mute frame features can be used to synchronize audio and video data. PTS audio extraction is also supported.

The device outputs up to 6 channels of PCM data and appropriate clocks for external digital-to-analog converters.

Programmable downmix enables 1,2,3 or 4 channel outputs. Data can be output in either I<sup>2</sup>S format or Sony format. The decoder can format output data according to IEC-60958 standard (for non compressed data: L/R channels, 16, 18, 20 and 24-bits) or IEC-61937 standard (for compressed data), for  $F_S = 96$  kHz, 48 kHz, 44.1 kHz or 32 kHz.

Sampling frequencies of 96 kHz, 48 kHz, 44.1 kHz, 32 kHz and half sampling frequencies are supported. A downsampling filter (96 kHz/48 kHz) is available.

The decoder supports dual mode for MPEG and Dolby Digital. It includes a Dolby surround compatible downmix and a ProLogic decoder.

A pink noise generator enables the accurate positioning of speakers for optimal surround sound setup.

PCM beep tone is a special mode used for Set Top Box. It generates a triangular signal of variable frequency and amplitude on the left and right channels.

In global mute mode, the decoder decodes the incoming bitstream normally but the PCM and SPDIF outputs are softmuted. This mode is used to prepare a period of decoding mode, to synchronize audio and video data without hearing the audio.

Slow-forward and fast-forward trick modes are available for compressed and non-compressed data.

The control interface of the decoder is activated via memory mapped registers in the ST20 address space.

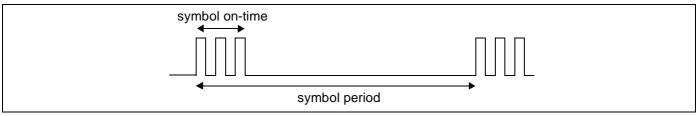

### 1.5 IR transmitter/receiver

67/

The STi5518 provides a pulse-position modulated signal for automatic VCR programming by the set-top box. The signal is output to the IR blast pin and an accessory jack pin, simultaneously. The pulse frequency, number of pulses (envelope length) and the total cycle time is controlled by registers.

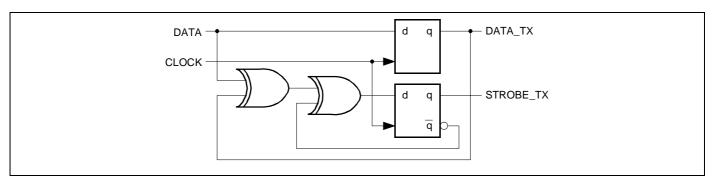

# 1.6 Modem analog front-end interface

The Modem Analog Front-end interface is used to transfer transmit and receive DAC and ADC samples between the memory and an external modem analog front-end (MAFE), using a synchronous serial protocol. DMA is used to transfer the sample data between memory buffers and the MAFE interface module, with separate transmit and receive buffers and double buffering of the buffer pointers. FIFOs are used to take into account the access latency to memory, in a worst case system and to allow the use of bursts for memory bandwidth efficiency improvement. The V22 bis standard is supported.

### **1** Architecture overview

# 1.7 Memory subsystem

### On-chip

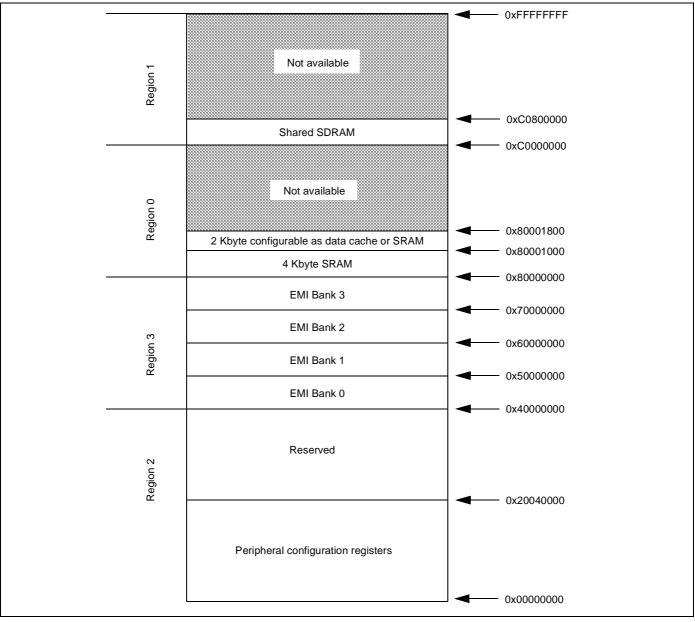

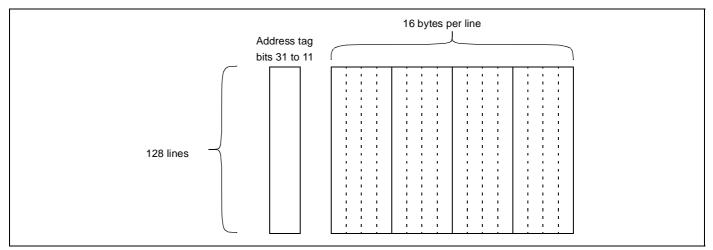

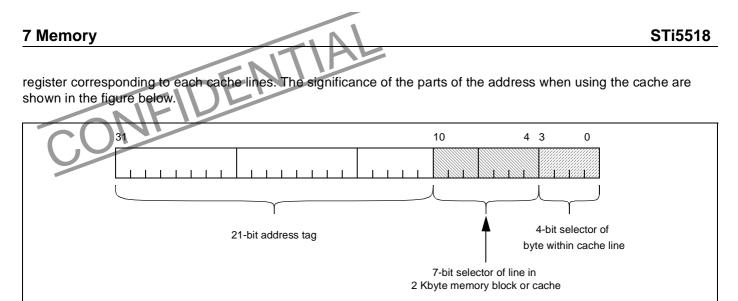

The on-chip memory includes 2Kbytes of instruction cache, 2Kbytes of data cache and 4Kbytes of SRAM that can be optionally configured as data cache. The subsystem provides 240M/bytes of internal bandwidth, supporting pipelined 2-cycle internal memory access.

The instruction and data caches are direct-mapped, with a write-back system for the data-cache. The caches support burst accesses to the external memories for refill and write-back. Burst access increases the performance of page-mode DRAM memories.

### Off-chip

There are two off-chip memory interfaces:

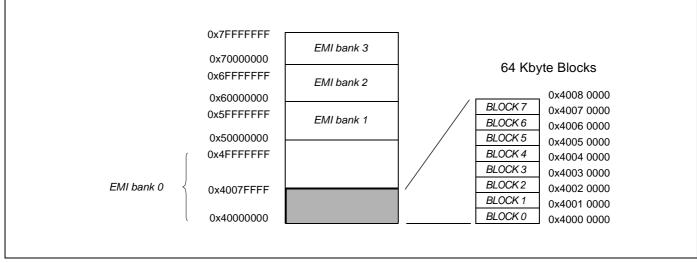

- The external memory interface (EMI) accessed by the ST20 is used for the transfer of data and programs between the STi5518 and external peripherals, flash and additional SDRAM and DRAM.

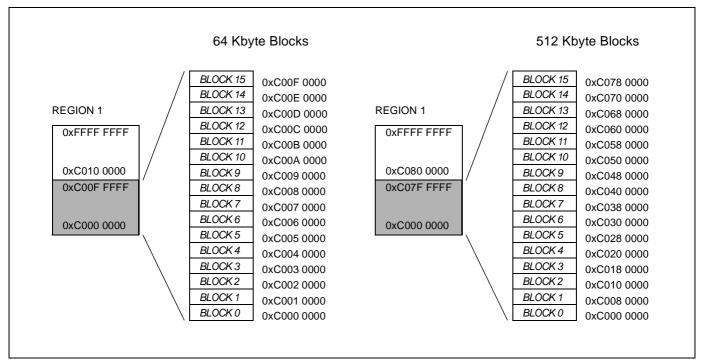

- Shared memory interface (SMI) controls the movement of data between the STi5518 and 16, 32 or 64 Mbits of SDRAM. This external SDRAM stores the display data generated by the MPEG decoder and CPU and the C2+ code data.

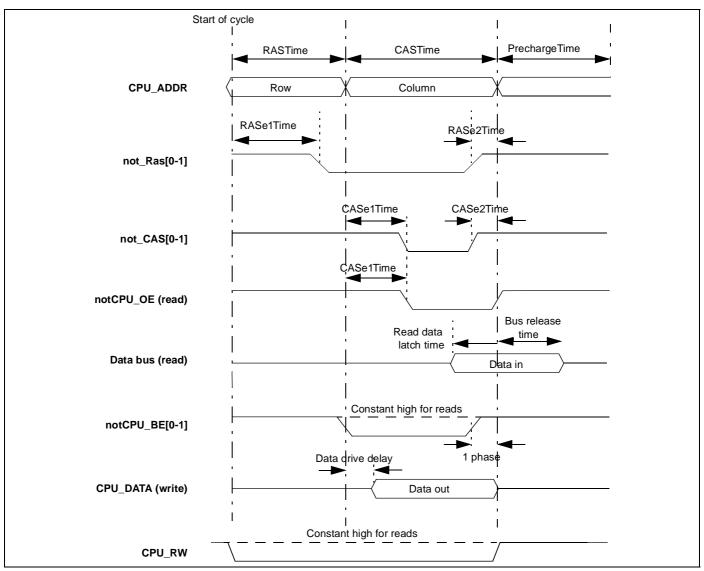

The EMI uses minimal external support logic to support memory subsystems, and accesses a 32 Mbytes of physical address space (greater if SDRAM or DRAM is used) in four general purpose memory banks of 8 or 16 bits wide, 21 or 22 address lines, and byte select. For applications requiring extra memory, the EMI supports this extra memory with zero external support logic, even for 16-bit SDRAM devices. The EMI can be configured for a wide variety of timing and decode functions by the configuration registers. The timing of each of the four memory banks can be set separately, with different device types being placed in each bank with no need for external hardware.

### 1.8 Serial communication

### Asynchronous serial controllers

The Asynchronous Serial Controller (ASC), also referred to as the UART interface, provides serial communication between the STi5518 and other microcontrollers, microprocessors or external peripherals. The STi5518 has four ASCs, two of which are generally used by the SmartCard controllers.

Eight or nine bit data transfer, parity generation, and the number of stop bits are programmable. Parity, framing, and overrun error detection increase data transfer reliability. Transmission and reception of data can be double-buffered, or 16-deep FIFOs can be used. A mechanism to distinguish the address from the data bytes is included for multiprocessor communication. Testing is supported by a loop-back option. A 16-bit baud-rate generator provides the ASC with a separate serial clock signal.

Two ASCs support full-duplex and 2 half-duplex asynchronous communication, where both the transmitter and the receiver use the same data frame format and the same baud rate. Each ASC can be set to operate in SmartCard mode for use when interfacing to a SmartCard.

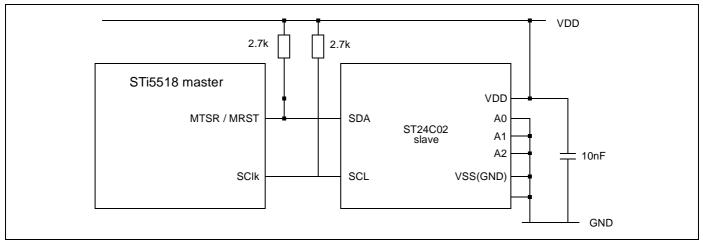

### Synchronous serial controller

Two Synchronous Serial Controllers (SSC) provide high-speed interfaces to a wide variety of serial memories, remote control receivers and other microcontrollers. The SSCs support all of the features of the Serial Peripheral Interface bus (SPI) and the I<sup>2</sup>C bus. The SSCs can be programmed to interface to other serial bus standards. The SSCs share pins with the parallel input/output (PIO) ports, and support half-duplex synchronous communication.

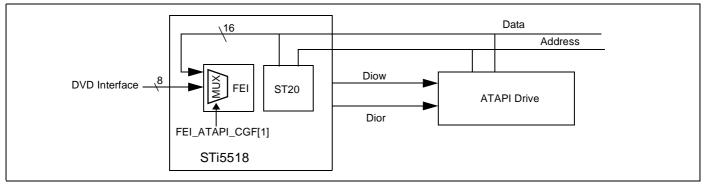

# 1.9 Front-end interface

The STi5518 can be connected to a front-end through the following interfaces:

- I<sup>2</sup>S interface;

- multi-format serial interface;

- multi-format parallel interface;

- ATAPI interface (for Hard Disk Drives and DVD-ROMs)

# 1.10 On-chip PLL

The on-chip PLL accepts 27 MHz input and generates all the internal high-frequency clocks needed for the CPU, MPEG and audio subsystems.

# 1.11 Diagnostic controller (DCU)

The ST20 Diagnostic Controller Unit (DCU) is used to boot the CPU and to control and monitor the chip systems via the standard IEEE 1194.1 Test Access Port. The DCU includes on-chip hardware with ICE (In Circuit Emulation) and LSA (Logic State Analyzer) features to facilitate verification and debugging of software running on the on-chip CPU in real time. It is an independent hardware module with a private link from the host to support real-time diagnostics.

# 1.12 Interrupt subsystem

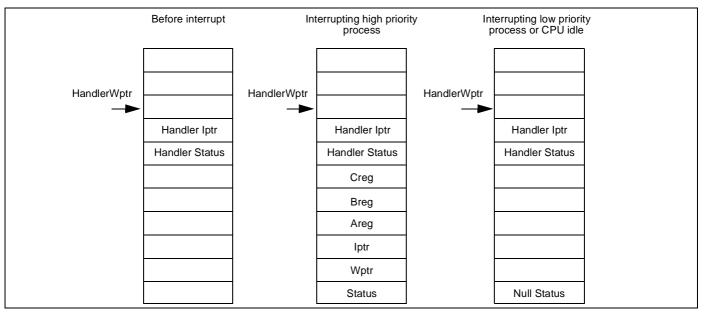

The interrupt system allows an on-chip module or external interrupt pin to interrupt an active process so that an interrupt handling process can be run. An interrupt can be signalled by one of the following: a signal on an external interrupt pin, a signal from an internal peripheral or subsystem, software asserting an interrupt in the pending register.

Interrupts are implemented by an on-chip interrupt controller and an on-chip interrupt-level controller. The interrupt controller supports eight prioritized interrupts as inputs and manages the pending interrupts. This allows the nesting of pre-emptive interrupts for real-time system design. Each interrupt can be programmed to be at a lower or higher priority than the high priority process queue.

# 1.13 PAL/NTSC/SECAM encoder

The integrated digital encoder converts a multiplexed 4:2:2 or 4:4:4 YCbCr stream into a standard analog baseband PAL/NTSC or SECAM signal and into RGB, YUV, Yc and CVBS components. The encoder can perform closed-caption, CGMS encoding, and allows Macrovision<sup>TM</sup> 7.01/6.1 copy protection.

The DENC is able to encode Teletext according to the "CCIR/ITU-R Broadcast Teletext System B" specification, also known as "World System Teletext".

In DVB applications, Teletext data is embedded within DVB streams as MPEG data packets. It is the responsibility of the software to handle incoming data packets and in particular to store Teletext packets in a buffer, which then passes them to the DENC on request.

# **1.14 SmartCard interfaces**

Two SmartCard interfaces support SmartCards compliant with ISO7816-3. Each interface is has a UART (ASC), a dedicated programmable clock generator, and eight bits of parallel IO port.

# 1.15 PWM and counter module

The PWM and counter module provides three PWM encoder outputs, three PWM decoder (capture) inputs and four programmable timers. Each capture input can be programmed to detect rising edge, falling edge, both edges or neither edge (disabled). These facilities are clocked by two independent clocks, one for PWM outputs and one for capture inputs/timers. The PWM counter is 8-bit, with 8-bit registers to set the output-high time. The capture/compare counter and the compare and capture registers are 32-bit. The module generates a single interrupt signal.

# 1.16 Parallel I/O module

44 bits of parallel I/O are configured in 6 ports, and each bit is programmable as output or input. The output can be configured as a totem-pole or open-drain driver. The input compare logic can generate an interrupt on any change of any input bit. Many parallel IO have alternate functions and can be connected to an internal peripheral signal such as a UART or SSC.

10

# 2.2 Pin list sorted by function

Alternate functions printed in *Italic* show a suggested use of the PIO; alternate functions not printed in *Italic* are multiplexed with a specific hardware.

|               | Pin name    | Main function             | Alternate function               |                         | <b>T</b>    |

|---------------|-------------|---------------------------|----------------------------------|-------------------------|-------------|

| Pin number    |             |                           | Input                            | Output                  | Туре        |

| Audio DAC     |             |                           |                                  |                         |             |

| 51            | DAC_SCLK    | over sampling clock       |                                  | EXT_AUD_CLK             | 0           |

| 52            | DAC_PCMOUT0 | PCM output 0              |                                  | EXT_AUD_DATA            | 0           |

| 53            | DAC_PCMOUT1 | PCM output 1              | EXT_AUD_REQ                      |                         | I/O         |

| 54            | DAC_PCMOUT2 | PCM output 2              |                                  |                         | 0           |

| 55            | DAC_PCMCLK  | PCM clock                 |                                  |                         | I/O         |

| 56            | DAC_LRCLK   | Left/right clock          |                                  | EXT_AUD_WCLK            | 0           |

| 57            | SPDIF_OUT   | SPDIF output              |                                  |                         | 0           |

| 48            | VDD_PCM     | VDD freq synthesizer=2.5V |                                  |                         | PWR<br>2.5V |

| 49            | VSS_PCM     | VSS freq synthesizer=GND  |                                  |                         | PWR         |

| Clock & reset |             |                           |                                  |                         | ÷           |

| 124           | RESET       | Chip reset                |                                  |                         | I           |

| 122           | VDD_PLL     | VDD PLL=2.5V              |                                  |                         | PWR<br>2.5V |

| 123           | VSS_PLL     | GND PLL=GND               |                                  |                         | PWR         |

| 120           | PIX _CLK    | 27 MHz main clock         |                                  |                         | I           |

| PIOs and com  | munication  |                           |                                  |                         |             |

| 186           | PIO0[0]     | PIO0[0]                   | UARTO_DATA (SCO_DAT              | 7A)                     | I/O         |

| 187           | PIO0[1]     | PIO0[1]                   | TTX_IN_CLOCK                     | ATAPI_RD                | I/O         |

| 188           | PIO0[2]     | PIO0[2]                   |                                  | ATAPI_WR                | I/O         |

| 189           | PIO0[3]     | PIO0[3]                   |                                  | SC0_CLOCK               | I/O         |

| 190           | PIO0[4]     | PIO0[4]                   |                                  | SC0_RST                 | I/O         |

| 191           | PIO0[5]     | PIO0[5]                   |                                  | SC0_CMD_VCC             | I/O         |

| 192           | PIO0[6]     | PIO0[6]                   |                                  | SC0_DATA_DIR            | I/O         |

| 193           | PIO0[7]     | PIO0[7]                   | SC0_DETECT                       |                         | I/O         |

| 194           | PIO1[0]     | PIO1[0]                   | SSC0_DATA (MTSROut/              | /MRSTin)                | I/O         |

| 195           | PIO1[1]     | PIO1[1]                   | SSC0_CLOCK                       |                         | I/O         |

| 196           | PIO1[2]     | PIO1[2]                   | SC EXTERNAL CLOCK<br>PARA_DVALID |                         | I/O         |

| 197           | PIO1[3]     | PIO1[3]                   |                                  | UART2_TXD               | I/O         |

| 200           | PIO1[4]     | PIO1[4]                   | UART2_RXD                        |                         | I/O         |

| 201           | PIO1[5]     | PIO1[5]                   | PARA_SYNC                        | UART1_TXD               | I/O         |

| 202           | TRIGGER_IN  | Trigger input for DCU     |                                  |                         | I/O         |

| 203           | TRIGGER_OUT | Trigger output for DCU    |                                  |                         | I/O         |

| 204           | PIO2[0]     | PIO2[0]                   | UART3_DATA (SC1_DAT              | A)                      | I/O         |

| 205           | PIO2[1]     | PIO2[1]                   | UART1_RXD                        | MAFEIF_DOUT<br>PARA_REQ | I/O         |

| STi5518        |                      |                |                                  | 2 Pi                              | n data |

|----------------|----------------------|----------------|----------------------------------|-----------------------------------|--------|

|                |                      | NIA            | Alternate function               |                                   |        |

| Pin number     | iber Pin name        | Main function  | Input                            | Output                            | Туре   |

| 206            | PIQ2[2]              | PIO2[2]        | PARA_STR                         | MAFEIF_HC1                        | I/O    |

| 207            | PIO2[3]              | PIO2[3]        |                                  | SC1_CLOCK                         | I/O    |

| 208            | PIO2[4]              | PIO2[4]        |                                  | SC1_RST                           | I/O    |

| 1              | PIO2[5]              | PIO2[5]        |                                  | SC1_CMD_VCC                       | I/O    |

| 2              | PIO2[6]              | PIO2[6]        |                                  | SC1_DATA_DIR                      | I/O    |

| 3              | PIO2[7]              | PIO2[7]        | SC1_DETECT                       |                                   | I/O    |

| 6              | PIO3[0]              | PIO3[0]        | MAFEIF_SCLK<br>PARA_DATA{0]      |                                   | I/O    |

| 7              | PIO3[1]              | PIO3[1]        | MAFEIF_DIN<br>PARA_DATA[1]       |                                   | I/O    |

| 8              | PIO3[2]              | PIO3[2]        | MAFEIF_FSI<br>PARA_DATA[2]       |                                   | I/O    |

| 9              | PIO3[3]              | PIO3[3]        | CAPTURE_IN0<br>PARA_DATA[3]      |                                   | I/O    |

| 10             | PIO3[4]              | PIO3[4]        | CAPTURE_IN1<br>PARA_DATA[4]      | UART1 RTS (RTS1)                  | I/O    |

| 11             | PIO3[5]              | PIO3[5]        | CAPTURE_IN2<br>PARA_DATA[5]      | UART2 RTS (RTS2)                  | I/O    |

| 12             | PIO3[6]              | PIO3[6]        | PARA_DATA[6]<br>UART1 CTS (CTS1) | COMP_OUT1                         | I/O    |

| 13             | PIO3[7]              | PIO3[7]        | PARA_DATA[7]<br>UART2 CTS (CTS2) | COMP_OUT0                         | I/O    |

| 39-46          | PIO4[0:7]            | PIO4[0:7]      |                                  | YC[0:7]                           | I/O    |

| 20             | PIO5[0]              | PIO5[0]        | B_WCLK<br>SSC1_DATA/             | NRSS_CLOCK <sup>1</sup>           | I/O    |

| 21             | PIO5[1]              | PIO5[1]        | B_V4                             | NRSS_OUT <sup>2 and 1</sup>       | I/O    |

|                |                      |                | SSC1_                            | _CLOCK                            |        |

| 22             | PIO5[2]              | PIO5[2]        | IRB_IRinput/NRSS_IN <sup>2</sup> | 2                                 | I/O    |

|                |                      |                | SDAV_CLK                         | / P1394_Clk <sup>3</sup>          |        |

| 103            | PIO5[3] <sup>4</sup> | PIO5[3]        | IRB_UHFinput <sup>4</sup>        |                                   | I/O    |

|                |                      |                | SDAV                             | <br>DATA <sup>3</sup>             | -      |

| 104            | PIO5[4]              | PIO5[4]        |                                  | IRB_drivePPMsignal                | I/O    |

|                |                      |                |                                  | P1394_P_CLK <sup>3</sup>          | -      |

| 105            | PIO5[5]              | PIO5[5]        |                                  | IRB_drive0orZ <sup>5</sup> (jack) | I/O    |

|                |                      |                | OSC_I                            | IN_CLK <sup>3</sup>               |        |

| Auxiliary Cloc | k                    |                |                                  |                                   |        |

| 106            | Auxiliary Clock      |                |                                  |                                   | 0      |

| EMI Interface  |                      |                |                                  |                                   |        |

| 161-170        | CPU_ADR[1:10]        | Address[1:10]  |                                  |                                   | 0      |

| 173-183        | CPU_ADR[11:21]       | Address[11:21] |                                  |                                   | 0      |

| 141-148        | CPU_DATA[0:7]        | Data[0:7]      |                                  |                                   | I/O    |

| 2 Pin data |                   | THE                              |                                              |                                 | Ti55 <sup>,</sup> |

|------------|-------------------|----------------------------------|----------------------------------------------|---------------------------------|-------------------|

|            |                   |                                  | Alternate function                           |                                 |                   |

| Pin number | Pin name          | Main function                    | Input                                        | Output                          | Туре              |

| 151-158    | CPU_DATA[8:15]    | Data[8:15]                       |                                              |                                 | I/O               |

| 138        | CPU_RAS1          | DRAM RAS                         |                                              | NOT_SDRAM_CS1<br>CHIPSEL. BANK3 | I/O               |

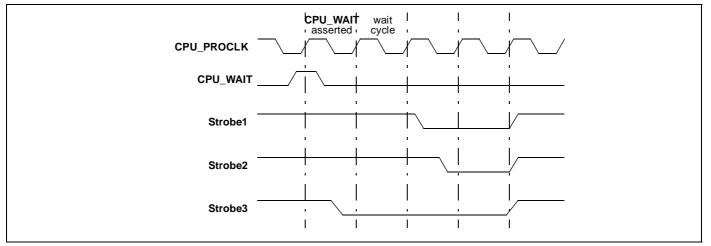

| 131        | CPU_WAIT          | Wait state                       |                                              |                                 | I                 |

| 130        | CPU_RW            | Read-not-write                   |                                              | NOT_SDRAM_WE                    | 0                 |

| 128        | CPU_BE[0]         | Byte 0 enable                    |                                              | DQM[0]                          | 0                 |

| 129        | CPU_BE[1]         | Byte 1 enable                    |                                              | DQM[1]                          | 0                 |

| 139        | CPU_CAS0          | DRAM CAS 0                       |                                              | SDRAM_CAS/<br>CPU_ADR[22]       | 0                 |

| 140        | CPU_CAS1          | DRAM                             |                                              | NOT_SDRAM_CS0                   | 0                 |

| 135        | CPU_CE[0]         | DRAM RAS 0                       |                                              | SDRAM_RAS<br>NOTCHIPSELBANK0    | 0                 |

| 134        | CPU_CE[1]         | Chip sel. bank 1                 |                                              |                                 | 0                 |

| 133        | CPU_CE[2]         | Chip sel. bank 2                 |                                              |                                 | 0                 |

| 132        | CPU_CE[3]         | Chip sel. bank 3                 |                                              | CS_SUB_BANK3                    | 0                 |

| 118        | CPU_PROCLK        | EMI clock                        |                                              |                                 | 0                 |

| 117        | CPU_OE            | Output enable                    |                                              |                                 | I/O               |

| Interrupt  |                   |                                  |                                              |                                 |                   |

| 127        | IRQ[0]            | IRQ[0] (SERVO_IRQ)               |                                              |                                 | I                 |

| 126        | IRQ[1]            | IRQ[1] (ATAPI IRQ)               |                                              |                                 | I                 |

| 125        | IRQ[2]            | IRQ[2] (MD_IRQ)                  |                                              |                                 | I                 |

| Timers     |                   |                                  |                                              |                                 |                   |

| 116        | PWM0              | Pulse Width Modulator 0          | HSYNC                                        |                                 | I/O               |

| 115        | PWM1              | Pulse Width Modulator 1          | BOOT_FROM_ROM <sup>6</sup>                   |                                 | I/O               |

| 114        | PWM2              | Pulse Width Modulator 2          | VSYNC                                        |                                 | I/O               |

| JTAG       |                   |                                  |                                              |                                 |                   |

| 113        | ТСК               | Test clock                       |                                              |                                 | I                 |

| 112        | TDI               | Test data in                     |                                              |                                 | I                 |

| 111        | TDO               | Test data out                    |                                              |                                 | 0                 |

| 110        | TMS               | Test mode select                 |                                              |                                 | I                 |

| 109        | TRST <sup>7</sup> | Test reset                       |                                              |                                 | I                 |

| Front-end  |                   |                                  |                                              |                                 |                   |

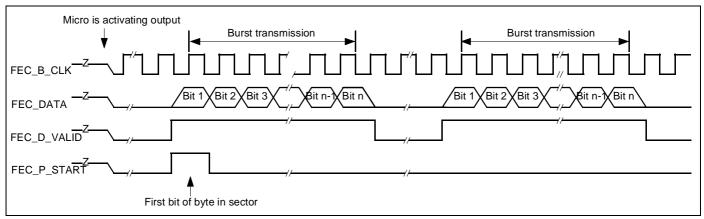

| 16         | B_DATA            | I <sup>2</sup> S data            | FEC_DATA                                     |                                 | I                 |

| 17         | B_BCLK            | I <sup>2</sup> S bit clock       | FEC_B_CLK                                    |                                 | 1                 |

| 18         | B_FLAG            | l <sup>2</sup> S error flag dvd  | FEC_D_VALID (DVD)<br>FEC_P_CLK (DVB/DSS)     |                                 | I                 |

| 19         | B_SYNC            | I <sup>2</sup> S sector/ABS time | FEC_P_START (DVD)<br>FEC_ERROR (DVB/<br>DSS) |                                 | I                 |

| Video DAC  |                   |                                  |                                              |                                 |                   |

| 27, 26, 25 | R_OUT, G_OUT, B O | UT R_OUT, G_OUT, B_OUT           |                                              |                                 | 0                 |

| STi5518                                                                       |                         |                           |                    |        | 2 Pin data  |

|-------------------------------------------------------------------------------|-------------------------|---------------------------|--------------------|--------|-------------|

|                                                                               |                         | XIT IF                    |                    |        |             |

|                                                                               | InF                     |                           | Alternate function |        |             |

| Pin number                                                                    | Pin name                | Main function             | Input              | Output | Туре        |

| 32, 33, 34                                                                    | Y_OUT, C_OUT,<br>CV_OUT | Y_OUT, C_OUT, CV_OUT      |                    |        | 0           |

| 29                                                                            | I_REF_RGB               | RGB DAC reference current |                    |        | I           |

| 28                                                                            | V_REF_RGB               | RGB DAC reference voltage |                    |        | 1           |

| 36                                                                            | I_REF_YCC               | YCC DAC reference current |                    |        | 1           |

| 35                                                                            | V_REF_YCC               | YCC DAC reference voltage |                    |        | 1           |

| 23                                                                            | VDD_RGB                 | VDDA_RGB=2.5V             |                    |        | PWR<br>2.5V |

| 24                                                                            | VSS_RGB                 | VSSA_RGB=GND              |                    |        | PWR         |

| 30                                                                            | VDD_YCC                 | VDDA_YCC=2.5V             |                    |        | PWR<br>2.5V |

| 31                                                                            | VSS_YCC                 | VSSA_YCC=GND              |                    |        | PWR         |

| Shared memor                                                                  | y interface             |                           |                    |        |             |

| 69-66                                                                         | SMI_ADR[0:3]            | Address bus SDRAM         |                    |        | 0           |

| 58-63                                                                         | SMI_ADR[4:9]            | Address bus SDRAM         |                    |        | 0           |

| 70-73                                                                         | SMI_ADR [10:13]         | Address bus SDRAM         |                    |        | 0           |

| 84-93, 97-102                                                                 | SMI_DATA[0:15]          | Data bus SDRAM            |                    |        | I/O         |

| 74, 75                                                                        | SMI_CS[0,1]             | Chip select bank 0,1      |                    |        | 0           |

| 76                                                                            | SMI_RAS                 | RAS SDRAM                 |                    |        | 0           |

| 77                                                                            | SMI_CAS                 | CAS SDRAM                 |                    |        | 0           |

| 78                                                                            | SMI_WE                  | SDRAM write enable        |                    |        | 0           |

| 79, 80                                                                        | SMI_DQML, U             | DQ mask en low, up        |                    |        | 0           |

| 82                                                                            | SMI_CLKIN               | SDRAM clock in            |                    |        | 1           |

| 95                                                                            | SMI_CLKOUT              | SDRAM clock out           |                    |        | 0           |

| Power supply                                                                  |                         |                           |                    |        |             |

| 4, 47, 81, 107,<br>136, 159, 184                                              | VDD3_3                  | 3.3 V POWER SUPPLY        |                    |        | PWR         |

| 14, 37, 64, 94,<br>119, 149, 171,<br>198                                      | VDD2_5                  | 2.5V POWER SUPPLY         |                    |        | PWR         |

| 5, 15, 38, 50,<br>65, 83, 96,<br>108, 121, 137,<br>150, 160, 172,<br>185, 199 | VSS                     | Ground                    |                    |        | PWR         |

- 1. FEI\_CFG bits 8 and 9 must be programmed according to the required NRSS configuration.

- 2. The NRSS\_IN and NRSS\_OUT pins are swapped around on the STi5518 compared to the STi5508.

- 3. Register LNK\_SDAV\_CONF bit 22 (SDE) must be set to 1 to validate the output path.

- 4. Inverted. ATTENTION! the PIO input is also inverted.

- 5. The PIO must be configured in open drain.

- 6. BOOT\_FROM\_ROM is active during reset.

- 7. Tie low whenever JTAG is not used.

# 2.3 Pins sorted by pin number

| Pin N° Pi | Din kanna | Main function                    | Alternate function                           |                             | Dir func. |

|-----------|-----------|----------------------------------|----------------------------------------------|-----------------------------|-----------|

| PINN      | Pin name  | Main function                    | Input                                        | Input Output                |           |

| Left Side | 9         |                                  |                                              |                             |           |

| 1         | PIO2[5]   | PIO2[5]                          |                                              | SC1_CMD_VCC                 | I/O       |

| 2         | PIO2[6]   | PIO2[6]                          |                                              | SC1_DATA_DIR                | I/O       |

| 3         | PIO2[7]   | PIO2[7]                          | SC1_DETECT                                   |                             | I/O       |

| 4         | VDD3_3    | 3.3 V power supply               |                                              |                             | POWER     |

| 5         | VSS       | Ground                           |                                              |                             | POWER     |

| 6         | PIO3[0]   | PIO3[0]                          | MAFEIF_SCLK<br>PARA_DATA{0]                  |                             | I/O       |

| 7         | PIO3[1]   | PIO3[1]                          | MAFEIF_DIN<br>PARA_DATA[1]                   |                             | I/O       |

| 8         | PIO3[2]   | PIO3[2]                          | MAFEIF_FSI<br>PARA_DATA[2]                   |                             | I/O       |

| 9         | PIO3[3]   | PIO3[3]                          | CAPTURE_IN0<br>PARA_DATA[3]                  |                             | I/O       |

| 10        | PIO3[4]   | PIO3[4]                          | CAPTURE_IN1 UART1 RTS (RTS1<br>PARA_DATA[4]  |                             | I/O       |

| 11        | PIO3[5]   | PIO3[5]                          | CAPTURE_IN2 UART2 RTS (RTS2<br>PARA_DATA[5]  |                             | I/O       |

| 12        | PIO3[6]   | PIO3[6]                          | PARA_DATA[6] COMP_OUT1<br>UART1 CTS (CTS1)   |                             | I/O       |

| 13        | PIO3[7]   | PIO3[7]                          | PARA_DATA[7] COMP_OUT0<br>UART2 CTS (CTS2)   |                             | I/O       |

| 14        | VDD2_5    | 2.5V power supply                |                                              |                             | POWER     |

| 15        | VSS       | Ground                           |                                              |                             | POWER     |

| 16        | B_DATA    | I <sup>2</sup> S data            | FEC_DATA                                     |                             | I         |

| 17        | B_BCLK    | I <sup>2</sup> S bit clock       | FEC_B_CLK                                    |                             | 1         |

| 18        | B_FLAG    | I <sup>2</sup> S error flag DVD  | FEC_D_VALID (DVD)<br>FEC_P_CLK (DVB/DSS)     |                             | I         |

| 19        | B_SYNC    | I <sup>2</sup> S sector/ABS time | FEC_P_START (DVD)<br>FEC_ERROR (DVB/<br>DSS) |                             | I         |

| 20        | PIO5[0]   | PIO5[0]                          | B_WCLK                                       |                             | I/O       |

|           |           |                                  | SSC1_DATA/ NI                                | RSS_CLOCK <sup>1</sup>      | 1         |

| 21        | PIO5[1]   | PIO5[1]                          | B_V4                                         | NRSS_OUT <sup>2 and 1</sup> | I/O       |

|           |           |                                  | SSC1_C                                       |                             |           |

| 22        | PIO5[2]   | PIO5[2]                          | IRB_IRinput/NRSS_IN <sup>2</sup>             |                             | I/O       |

|           |           |                                  | SDAV_CLK/ F                                  | 21394_CLK <sup>3</sup>      |           |

| 23        | VDD_RGB   | VDDA_RGB=2.5V                    |                                              |                             | POWER     |

| 24        | VSS_RGB   | VSSA_RGB=GND                     |                                              |                             | POWER     |

| 25        | B_OUT     | B output                         |                                              |                             | 0         |

| STi5518   | 3               |                           |                    | :            | 2 Pin data  |

|-----------|-----------------|---------------------------|--------------------|--------------|-------------|

|           |                 | -NTI-                     |                    |              |             |

|           |                 |                           | Alternate function |              |             |

| Pin N°    | Pin N° Pin name | Main function             | Input              | Output       | — Dir func. |

| 26        | G_OUT           | G output                  |                    |              | 0           |

| 27        | R_OUT           | R output                  |                    |              | 0           |

| 28        | V_REF_RGB       | RGB DAC reference voltage |                    |              | 1           |

| 29        | I_REF_RGB       | RGB DAC reference current |                    |              | I           |

| 30        | VDD_YCC         | VDDA_YCC=2.5V             |                    |              | POWER       |

| 31        | VSS_YCC         | VSSA_YCC=GND              |                    |              | POWER       |

| 32        | Y_OUT           | Y output                  |                    |              | 0           |

| 33        | C_OUT           | C output                  |                    |              | 0           |

| 34        | CV_OUT          | CV output                 |                    |              | 0           |

| 35        | V_REF_YCC       | YCC DAC reference voltage |                    |              | l           |

| 36        | I_REF_YCC       | YCC DAC reference current |                    |              | I           |

| 37        | VDD2_5          | 2.5V power supply         |                    |              | POWER       |

| 38        | VSS             | Ground                    |                    |              | POWER       |

| 39        | PIO4[0]         | PIO4[0]                   |                    | YC[0]        | I/O         |

| 10        | PIO4[1]         | PIO4[1]                   |                    | YC[1]        | I/O         |

| 11        | PIO4[2]         | PIO4[2]                   |                    | YC[2]        | I/O         |

| 42        | PIO4[3]         | PIO4[3]                   |                    | YC[3]        | I/O         |

| 43        | PIO4[4]         | PIO4[4]                   |                    | YC[4]        | I/O         |

| 14        | PIO4[5]         | PIO4[5]                   |                    | YC[5]        | I/O         |

| 45        | PIO4[6]         | PIO4[6]                   |                    | YC[6]        | I/O         |

| 46        | PIO4[7]         | PIO4[7]                   |                    | YC[7]        | I/O         |

| 17        | VDD3_3          | 3.3 V power supply        |                    |              | POWER       |

| 48        | VDD_PCM         | VDD freq synthesizer=2.5V |                    |              | POWER       |

| 19        | VSS_PCM         | VSS freq synthesizer=GND  |                    |              | POWER       |

| 50        | VSS             | Ground                    |                    |              | POWER       |

| 51        | DAC_SCLK        | Sampling clock            |                    | EXT_AUD_CLK  | 0           |

| 52        | DAC_PCMOUT0     | PCM output 0              |                    | EXT_AUD_DATA | 0           |

| Bottom si | de              |                           |                    |              |             |

| 53        | DAC_PCMOUT1     | PCM output 1              | EXT_AUD_REQ        |              | I/O         |

| 54        | DAC_PCMOUT2     | PCM output 2              |                    |              | 0           |

| 55        | DAC_PCMCLK      | PCM clock                 |                    |              | I/O         |

| 56        | DAC_LRCLK       | Left/right clock          |                    | EXT_AUD_WCLK | 0           |

| 57        | SPDIF_OUT       | SPDIF output              |                    |              | 0           |

| 58        | SMI_ADR[4]      | Address bus SDRAM         |                    |              | 0           |

| 59        | SMI_ADR[5]      | Adress bus SDRAM          |                    |              | 0           |

| 60        | SMI_ADR[6]      | Adress bus SDRAM          |                    |              | 0           |

| 61        | SMI_ADR[7]      | Adress bus SDRAM          |                    |              | 0           |

| 62        | SMI_ADR[8]      | Adress bus SDRAM          |                    |              | 0           |

| 63        | SMI_ADR[9]      | Adress bus SDRAM          |                    |              | 0           |

| 64        | VDD2_5          | 2.5V power supply         |                    |              | POWER       |

### 2 Pin data

| 2 Pin da        | ata           |                    |                           |                      | STi551 |

|-----------------|---------------|--------------------|---------------------------|----------------------|--------|

|                 |               |                    |                           |                      |        |

|                 |               | FIL                | Alternate function        |                      |        |

| Pin N° Pin name | Main function | Input              | Output                    | Dir func.            |        |

| 65              | VSS           | Ground             |                           |                      | POWER  |

| 66              | SMI_ADR[3]    | Adress bus SDRAM   |                           |                      | 0      |

| 67              | SMI_ADR[2]    | Adress bus SDRAM   |                           |                      | 0      |

| 68              | SMI_ADR[1]    | Adress bus SDRAM   |                           |                      | 0      |

| 69              | SMI_ADR[0]    | Adress bus SDRAM   |                           |                      | 0      |

| 70              | SMI_ADR[10]   | Adress bus SDRAM   |                           |                      | 0      |

| 71              | SMI_ADR[11]   | Adress bus SDRAM   |                           |                      | 0      |

| 72              | SMI_ADR[12]   | Adress bus SDRAM   |                           |                      | 0      |

| 73              | SMI_ADR[13]   | Adress bus SDRAM   |                           |                      | 0      |

| 74              | SMI_CS[0]     | Chip select bank 0 |                           |                      | 0      |

| 75              | SMI_CS[1]     | Chip select bank 1 |                           |                      | 0      |

| 76              | SMI_RAS       | RAS SDRAM          |                           |                      | 0      |

| 77              | SMI_CAS       | CAS SDRAM          |                           |                      | 0      |

| 78              | SMI_WE        | SDRAM write enable |                           |                      | 0      |

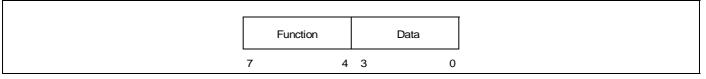

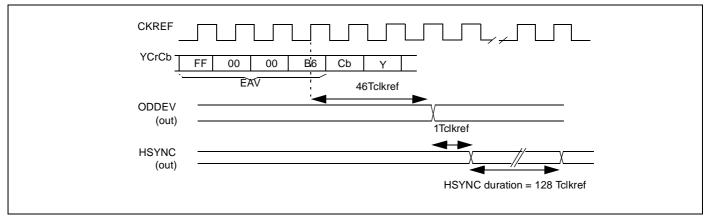

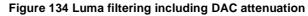

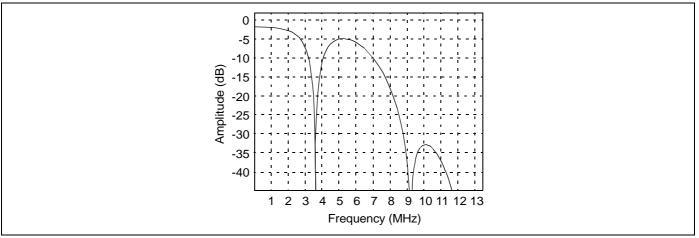

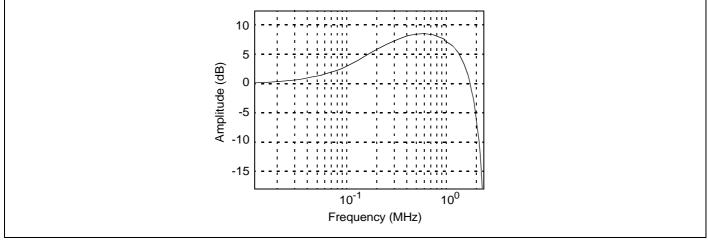

| 79              | SMI_DQML      | DQ mask en low     |                           |                      | 0      |